# Intel<sup>®</sup> Ethernet Controller I225/ I226

# Datasheet

#### General

- Integrated MAC/PHY supporting 10BASE-Te,100BASE-TX, 1000BASE-T and 2500BASE-T 802.3 specifications

- IEEE 802.3u auto-negotiation conformance

- Carrier extension support (half duplex)

- Half duplex operation at 10BASE-Te and 100BASE-TX

- Automatic polarity correction

- Network proxy/ARP offload

- MDC/MDIO management interface

- Smart speed operation for automatic speed reductionon faulty cable plants

- Power optimizer support

- Intel<sup>®</sup> Stable Image Platform Program (SIPP)

#### Interconnects

- 1 lane PCIe Gen 2 v3.1 interface for active state operation

- SMBus interface to Intel vPro<sup>®</sup> engine at low system power state

- Integrated MDI termination resistors reducing BOM costs

- Configurable MDI TAP up/down operation

- Three configurable LED outputs

#### Package & Design

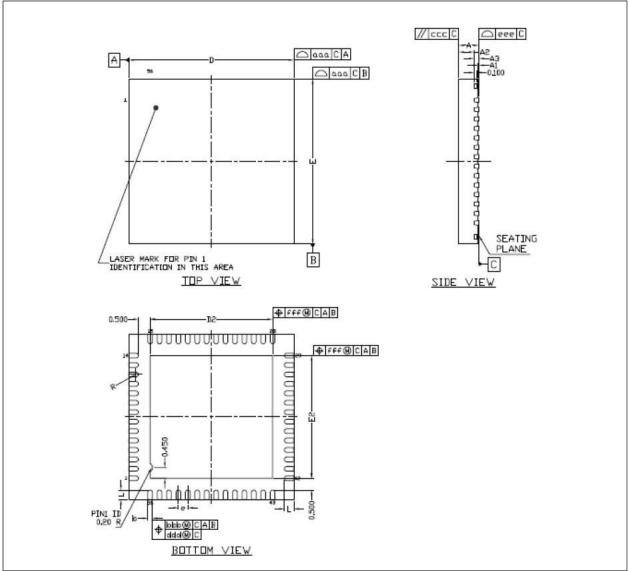

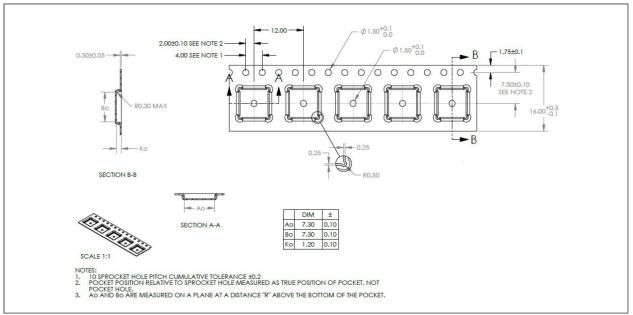

- 7x7 mm PG-VQFN-56 with a 0.4 mm lead pitch and an Exposed Pad\* for ground

- Commercial temperature: 0 °C to +70 °C

- I225-IT Extended temperature:

- 2.5G: -40 °C to +70 °C

- 10M/100M/1G: -40 °C to +85 °C

- I226-IT Industrial temperature:

- 10M/100M/1G/2.5G: -40 °C to +85 °C

- Integrated Switching Voltage Regulator (iSVR)

#### **Advanced Features**

- Error Correcting Memory (ECC) in packet buffers

- UDP, TCP and IP checksum offload

- UDP and TCP Transmit Segmentation Offload (TSO)

- SCTP receive and transmit integrity offload

- Queues: 4 Tx and 4 Rx queues

- PXE Support:

- I225: Legacy PXE (minimal support) and EFI PXE

- I226: EFI PXE only

#### Time Sensitive Networking (TSN) – FDX Network

- IEEE 1588 Basic time-sync (Precision Time Protocol)

- IEEE 802.1AS-Rev Higher precision time

- synchronization with multiple (dual) clock mastersIEEE 802.1Qav Credit Based Shaping and Basicscheduling

- IEEE 802.1Qbu Frame Preemption

- IEEE 802.1Qbv Time Aware Shaper

- IEEE 802.3br Interspersing Express Traffic

- PCIe PTM for synchronization between the NIC and Host timers

#### Performance

- Four transmit and four receive queues

- Jumbo frames (up to 9 KB and without TSN)

- Receive Side Scaling (RSS) and MSI-X to lower CPU use in multi-core systems

#### Power

- IEEE 802.3az Energy Efficient Ethernet (EEE) I226 only

- Ultra-low power at cable disconnected (18 mW) I226 only

- Single-pin LAN disable for easier BIOS implementation

- Modern standby system support

- Advanced Configuration and Power Interface (ACPI) power management states and wake-up capability

- Advanced Power Management (APM) wake-up functionality

- Low power link up state

- PCIe v2.1 Latency Tolerance Reporting (LTR)

- PCIe v3.1 L1 sub-states

- DMA coalescing for improved system power management

#### Security & Manageability

- Authenticated Flash image

- Flash wear-out protection

- Intel<sup>®</sup> vPro support with appropriate Intel chipset

- MCTP over PCIe and over SMBus

#### Others

• For operating systems and SKU features breakdown, refer to the I225/226 Message of the Week (MOW)

# **Revision History**

| Revision | Date            | Comments                                                                 |

|----------|-----------------|--------------------------------------------------------------------------|

| 2.6      | February 2022   | Update table 1-1, table 1-6, chapter 1.2, 3.6, 3.6.1, 4.1                |

| 2.0      | 1 00.001 / 2022 | Update 7.2.2 Recommended Operating Conditions                            |

| 2.5.2    | November 2021   | Update the media type on chapter 8.7                                     |

| 2.5.1    | November 2021   | Update the description on pin 34 and pin 37 in table 2-5                 |

|          |                 | Adding I226                                                              |

|          |                 | Added Device ID Table                                                    |

| 2.5      | October 2021    | Updated Power Consumption Table                                          |

|          |                 | Updated Default SMBUS Slave Address                                      |

|          |                 | Updated image for figure 3-1 NMV Structure<br>Updated title page.        |

|          |                 | 1 1 0                                                                    |

|          |                 | Changed industrial temperature information to extended temperature.      |

|          |                 | Updated Ethernet media interface.                                        |

|          |                 | Added note for SMBus resistor pull-up value.                             |

|          |                 | Added default SMBus slave address.                                       |

|          |                 | Added general power state information.                                   |

| 2.0      | October 2020    | Updated BOM list (to support extended temperature applications). Updated |

|          |                 | order information.                                                       |

|          |                 | Added new section (2.7.1; Leakage Avoidance on LAN Power Disconnect).    |

|          |                 | Updated title page (commercial/industrial temp values). Revised          |

| 1.92     | March 2020      | table 7.2.2 (recommended operating conditions).                          |

| 1.91     | March 2020      | Initial Release.                                                         |

# 1.0 Introduction

The Intel<sup>®</sup> 2.5 Gigabit Ethernet Controller I225/I226 is a single-port, compact, low power Gigabit Ethernet (GbE) controller. It is a fully integrated GbE Media Access Control (MAC) and Physical Layer (PHY) device, offering 10/100/1000/2500 Mb/s data rates. The interface-to-host system is a one lane PCI Express\* (PCIe\*) Gen 2 (5.0GT/s) version 3.1.

*Note:* I225 v1 (B1 stepping) reaches 2.5 GbE on select switches/routers. Refer to the *Intel® Ethernet Controller I225 Public External Specification Update* for more detail.

## 1.1 Feature Summary

The I225/I226 enables 2.5 GbE BASE-T implementations using an integrated MAC/PHT architecture. It can be used for client systems, server systems and dock configurations such as desktop, laptops, workstations, server, Thunderbolt<sup>™</sup> dock in add-on Network Interface Card (NIC) or LAN on Motherboard (LOM) designs.

The I225/I226 is packaged in a small footprint VQFN package. Package size is 7 x 7 mm with a 0.4 mm lead pitch and a height of 0.85 mm, making it very attractive for small form-factor platforms.

The I225/I226 supports the Intel vPro<sup>®</sup>. The interface to the vPro<sup>®</sup> engine is over SMBus as well as the PCIe link at active system state.

The I225/I226 also supports a Time Sensitive Network (TSN) that can be used in Audio/Video Bridging (AVB) applications and extended temperature applications that require TSN capabilities.

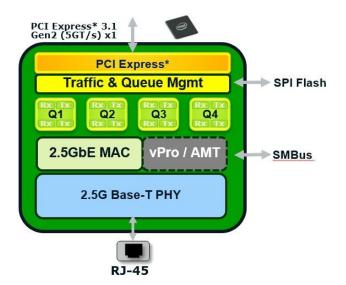

Figure 1-1. I225/I226 High level Functional View

### 1.1.1 Ethernet Interface

The I225/I226 implements an IEEE 802.3 MII Management Interface, also known as the Management Data Input / Output (MDIO interface), to the internal PHY. This interface provides the MAC and software the ability to monitor and control the state of the PHY. The MDIO interface defines a special protocol that runs across the connection, and an internal set of addressable registers. The interface consists of internal data line (MDIO) and clock line (MDC), which are accessible by software via the MAC register space.

### 1.1.2 Intel vPro<sup>°</sup> Interfaces

When the system is at its active state, the I225/I226 communicates with the Intel vPro<sup>®</sup> engine over PCIe. When the system is at low power state (Sx), the I225/I226 communicates with the Intel vPro<sup>®</sup> engine over SMBus. The I225/I226 and the Intel vPro<sup>®</sup> engine switch between these two interfaces according to the system power states (identified by the PCIe bus state).

The I225/I226 supports the SMBus at 1 MHz. This interface includes these open-drain signals:

- Data In/Out signal SMB\_DATA

- Clock signal SMB\_CLK

Default SMBUS Slave Address:

- 0x59 (address 0xB2) for LOM/Discrete/NIC design.

- 0x49 (address 0x92) for Docking Station design.

#### 1.1.3 Configurable Software-Definable Pins (SDPs)

The I225/I226 also provides Software Defined Pins (SDPs) that can be used to drive or sense signals between external devices and the I225/I226. The SDP pin can be driven or sensed by the I225/I226 software or can be activated by the embedded 1588 timers.

#### 1.1.4 Feature Summary

Table 1-1 through Table 1-6 lists the feature set provided by the I225/I226.

#### Table 1-1. General Features

| Feature                                                                         | 1225/1226 |  |

|---------------------------------------------------------------------------------|-----------|--|

| Serial Flash interface                                                          |           |  |

| Configurable LED operation for software or OEM custom-tailoring of LED displays |           |  |

| Protected Flash space for private configuration                                 |           |  |

| Package size (mm x mm)                                                          |           |  |

| Extended temperature (special SKU)                                              |           |  |

| Industrial temperature (special SKU)                                            | I226IT    |  |

#### Table 1-2. Network Features

| Feature                                                                                | 1225/1226 |  |  |

|----------------------------------------------------------------------------------------|-----------|--|--|

| 2.5 Gbps BASE-T                                                                        | Y         |  |  |

| 10BASE-Te, 100BASE-TX, 1000BASE-T                                                      | Y         |  |  |

| Integrated BASE-T PHY                                                                  | Y         |  |  |

| MDI lane swap                                                                          | Y         |  |  |

| Half duplex at 10/100 Mb/s operation and full duplex operation at all supported speeds | Y         |  |  |

| Jumbo frames support (with no TSN)                                                     | Y         |  |  |

| Size of jumbo frames support                                                           | 9.5 KB    |  |  |

| Flow control support: send/receive PAUSE frames and receive FIFO thresholds            |           |  |  |

| 802.1q VLAN support                                                                    |           |  |  |

| 802.3az EEE support                                                                    | Y         |  |  |

#### Table 1-3. Host Interface Features

| Feature                                                                    | 1225/1226          |  |

|----------------------------------------------------------------------------|--------------------|--|

| PCle* revision                                                             | 3.1                |  |

| PCIe* physical layer                                                       | Gen 2<br>(5.0GT/s) |  |

| PCle* Bus width                                                            | x1                 |  |

| 64-bit address support for systems using more than 4 GB of physical memory |                    |  |

| CSR access via configuration space                                         |                    |  |

| TSN preemption, time aware shaper and interspersing                        | Y                  |  |

#### Table 1-4. LAN Function Features

| Feature                                                                          | 1225/1226 |  |  |  |  |

|----------------------------------------------------------------------------------|-----------|--|--|--|--|

| Programmable host memory receive buffers                                         |           |  |  |  |  |

| Descriptor ring management hardware for transmit and receive                     | Y         |  |  |  |  |

| ACPI register set and power down functionality supporting D0 and D3 states       | Y         |  |  |  |  |

| Wake up                                                                          | Y         |  |  |  |  |

| Flexible wake-up filters                                                         | 32        |  |  |  |  |

| Flexible filters for queue assignment in normal operation                        | 8         |  |  |  |  |

| IPv6 wake-up filters                                                             | Y         |  |  |  |  |

| Default configuration by the NVM Flash for all LEDs for pre-driver functionality | 3 LEDs    |  |  |  |  |

| Programmable memory transmit buffers                                             | Y         |  |  |  |  |

| Double VLAN                                                                      | Y         |  |  |  |  |

| IEEE 1588                                                                        | Y         |  |  |  |  |

| Per-packet time stamp                                                            | Y         |  |  |  |  |

| Tx rate limiting per queue                                                       | Y         |  |  |  |  |

#### Table 1-5.LAN Performance Features

| Feature                                                                                  |   |  |  |  |  |

|------------------------------------------------------------------------------------------|---|--|--|--|--|

| TCP segmentation offload Up to 256 KB                                                    | Y |  |  |  |  |

| IPv6 support for IP/TCP and IP/UDP receive checksum offload                              | Y |  |  |  |  |

| Fragmented UDP checksum offload for packet reassembly                                    | Y |  |  |  |  |

| Message Signaled Interrupts (MSI)                                                        | Y |  |  |  |  |

| Message Signaled Interrupts (MSI-X) number of vectors                                    | 5 |  |  |  |  |

| Interrupt throttling control to limit maximum interrupt rate and improve CPU utilization | Y |  |  |  |  |

| Rx packet split header                                                                   | Y |  |  |  |  |

| Total number of Rx queues                                                                | 4 |  |  |  |  |

| Total number of TX queues                                                                | 4 |  |  |  |  |

| TSO interleaving for reduced latency                                                     | Y |  |  |  |  |

| SCTP receive and transmit checksum offload                                               | Y |  |  |  |  |

#### Table 1-6. Power Management Features

| Feature                                                                    | 1225/ 1226 |  |  |

|----------------------------------------------------------------------------|------------|--|--|

| ACPI register set and power down functionality supporting D0 and D3 states |            |  |  |

| Full wake-up support (APM and ACPI 2.0)                                    | Y          |  |  |

| Smart power down at S0 no link and Sx no link                              |            |  |  |

| PCIe function disable                                                      | Y          |  |  |

| Dynamic device off                                                         | Y          |  |  |

| Energy Efficient Ethernet (EEE)                                            | I226 only  |  |  |

| DMA coalescing                                                             | Y          |  |  |

| Integrated SVR / LVR control                                               | Y          |  |  |

# 1.2 Intel <sup>®</sup> Ethernet Controller I226 - Highlights

Compared to I225, the I226 highlights state below:

- Dramatically reduced power consumption in all silicon states (20-50% reduction)

- Improved cable BER performance, especially on longer cables

- Ability to support industrial temperature fully (85°C) at 2.5G speeds

- Resolution for minor bug fixes, enhancements.

- Please review Intel<sup>®</sup> Ethernet Controller I225 Specification Update (<u>Content ID 615084</u>).

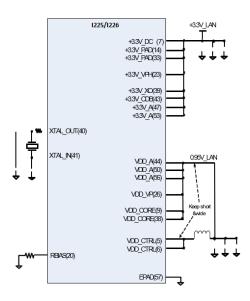

# 2.0 Pin Interface

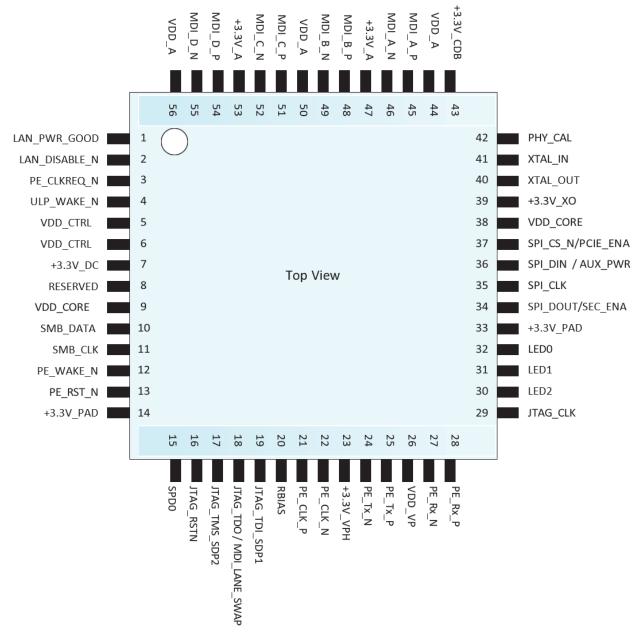

The I225/I226 is a 56-pin, 7 x 7 mm VQFN package. A top level view of the pin layout is shown in Figure 2-1. The I/O pins are listed in Table 2-1.

Figure 2-1. I225/I226 Pin Diagram (Top View)

#### Table 2-1. I225/I226 Pin List

| Pin # | Pin Name                   | Internal<br>Weak Pull<br>Up/Down<br>on Reset | Internal Weak<br>Pull Up/Down<br>During Normal<br>Operation |   | Pin #           | Pin Name           | Internal<br>Weak Pull<br>Up/Down<br>on Reset | Internal Weak<br>Pull Up/Down<br>During Normal<br>Operation |

|-------|----------------------------|----------------------------------------------|-------------------------------------------------------------|---|-----------------|--------------------|----------------------------------------------|-------------------------------------------------------------|

| 1     | LAN_PWR_GOOD               | PU                                           | PU                                                          |   | 29              | JTAG_CLK           | PU                                           | PU                                                          |

| 2     | LAN_DISABLE_N              | PU                                           | PU                                                          |   | 30              | LED2               | PU                                           |                                                             |

| 3     | PE_CLKREQ_N                | PU                                           |                                                             |   | 31              | LED1               | PU                                           |                                                             |

| 4     | ULP_WAKE_N                 | PU                                           |                                                             |   | 32              | LEDO               | PU                                           |                                                             |

| 5     | VDD_CTRL                   |                                              |                                                             |   | 33              | +3.3V_PAD          |                                              |                                                             |

| 6     | VDD_CTRL                   |                                              |                                                             |   | 34 <sup>1</sup> | SPI_DOUT/ SEC_ENA  | PU                                           | PU                                                          |

| 7     | +3.3V_DC                   |                                              |                                                             |   | 35 <sup>1</sup> | SPI_CLK            | PU                                           | PU                                                          |

| 8     | RESEVRED                   |                                              |                                                             |   | 36 <sup>1</sup> | SPI_DIN/AUX_PWR    | PU                                           | PU                                                          |

| 9     | VDD_CORE                   |                                              |                                                             |   | 37 <sup>1</sup> | SPI_CS_N/ PCIE_ENA | PU                                           | PU                                                          |

| 10    | SMB_DATA                   | PU                                           |                                                             |   | 38              | VDD_CORE           |                                              |                                                             |

| 11    | SMB_CLK                    | PU                                           |                                                             |   | 39              | +3.3V_XO           |                                              |                                                             |

| 12    | PE_WAKE_N                  | PU                                           |                                                             |   | 40              | XTAL_OUT           |                                              |                                                             |

| 13    | PE_RST_N                   | PU                                           | PU                                                          |   | 41              | XTAL_IN            |                                              |                                                             |

| 14    | +3.3V_PAD                  |                                              |                                                             |   | 42              | PHY_CAL            |                                              |                                                             |

| 15    | SDP0                       | PU                                           | PU                                                          |   | 43              | +3.3V_CDB          |                                              |                                                             |

| 16    | JTAG_RSTN                  | PD                                           | PD                                                          |   | 44              | VDD_A              |                                              |                                                             |

| 17    | JTAG_TMS_SDP2              | PU                                           | PU                                                          |   | 45              | MDI_A_P            |                                              |                                                             |

| 18    | JTAG_TDO/<br>MDI_LANE_SWAP | PU                                           | PU                                                          |   | 46              | MDI_A_N            |                                              |                                                             |

| 19    | JTAG_TDI_SDP1              | PU                                           | PU                                                          |   | 47              | +3.3V_A            |                                              |                                                             |

| 20    | RBIAS                      |                                              |                                                             |   | 48              | MDI_B_P            |                                              |                                                             |

| 21    | PE_CLK_P                   |                                              |                                                             |   | 49              | MDI_B_N            |                                              |                                                             |

| 22    | PE_CLK_N                   |                                              |                                                             |   | 50              | VDD_A              |                                              |                                                             |

| 23    | +3.3V_VPH                  |                                              |                                                             | 1 | 51              | MDI_C_P            |                                              |                                                             |

| 24    | PE_Tx_N                    |                                              |                                                             |   | 52              | MDI_C_N            |                                              |                                                             |

| 25    | PE_Tx_P                    |                                              |                                                             |   | 53              | +3.3V_A            |                                              |                                                             |

| 26    | VDD_VP                     |                                              |                                                             |   | 54              | MDI_D_P            |                                              |                                                             |

| 27    | PE_Rx_N                    |                                              |                                                             |   | 55              | MDI_D_N            |                                              |                                                             |

| 28    | PE_Rx_P                    |                                              |                                                             | 1 | 56              | VDD_A              |                                              |                                                             |

1. The internal pull-ups are weak. They should not be used for the normal operation. It is recommended that these pins have external pull-ups as needed.

# 2.1 Signal Type Definition (Abbreviations)

### Table 2-2.I/O Pin Type Abbreviations

| Abbreviations | Description                                 |  |

|---------------|---------------------------------------------|--|

| I             | Input-only, digital levels.                 |  |

| 0             | Output-only, digital levels.                |  |

| I/O           | Bidirectional In/Out digital levels signal. |  |

| Prg           | Programmable Bidirectional digital levels.  |  |

| PWR           | Power.                                      |  |

| AI            | Input-only, analog levels.                  |  |

| AO            | Output-only, analog levels.                 |  |

| AI/O          | Bidirectional, analog levels.               |  |

| GND           | Ground.                                     |  |

# 2.2 Ethernet Media Interface

### Table 2-3.Ethernet Media Interface

| Pin # | Pin Name | Pin Type                                 | MDI_LANE_<br>SWAP = 1<br>Functionality | MDI_LANE_<br>SWAP = 0<br>Functionality | Function                                                             |

|-------|----------|------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------------------------------------|

| 45    | MDI_A_P  | AI / AO                                  | MDI_A_P                                | MDI_D_N                                |                                                                      |

| 46    | MDI_A_N  | AI / AO                                  | MDI_A_N                                | MDI_D_P                                |                                                                      |

| 48    | MDI_B_P  | AI / AO                                  | MDI_B_P                                | MDI_C_N                                | Media Dependent Interface.<br>Connect four MDI pairs directly to the |

| 49    | MDI_B_N  | AI / AO                                  | MDI_B_N                                | MDI_C_P                                |                                                                      |

| 51    | MDI_C_P  | AI / AO                                  | MDI_C_P                                | MDI_B_N                                | magnetics/RJ45 component.                                            |

| 52    | MDI_C_N  | AI / AO                                  | MDI_C_N                                | MDI_B_P                                | No external terminations are needed.                                 |

| 54    | MDI_D_P  | AI / AO                                  | MDI_D_P                                | MDI_A_N                                | 7                                                                    |

| 55    | MDI_D_N  | AI / AO                                  | MDI_D_N                                | MDI_A_P                                |                                                                      |

| 42    | PHY_CAL  | Calibration for all GPHY Ethernet ports. |                                        |                                        |                                                                      |

# 2.3 PCIe Interface

#### Table 2-4.PCIe Interface

| Pin # | Pin Name    | Pin Type | Function                                                                                                                    |

|-------|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------|

| 28    | PE_Rx_P     | AI       | Differential PCIe Receive Pair. These                                                                                       |

| 27    | PE_Rx_N     | AI       | pins must be AC-coupled.                                                                                                    |

| 25    | PE_Tx_P     | AO       | Differential PCIe Transmit Pair. These                                                                                      |

| 24    | PE_Tx_N     | AO       | pins must be AC-coupled.                                                                                                    |

| 20    | RBIAS       | AI/O     | Pad to connect external tuning resistor.                                                                                    |

| 21    | PE_CLK_P    | AI       | Differential PCIe Clock Pair.                                                                                               |

| 22    | PE_CLK_N    | AI       | The input clock is 100 MHz external reference clock used by the PHY.                                                        |

| 13    | PE_RST_N    | I        | PCIe Reset.<br>Power and Clock Good Indication. The PE_RST_N signal indicates that both PCIe power and clock are available. |

| 12    | PE_WAKE_N   | I/O      | PCIe Wake.<br>This signal is driven to zero (0V) when it detects a wake-up event and either:                                |

| 3     | PE_CLKREQ_N | 1/0      | PCIe Clock Request.<br>This PCIe CLKREQ# is for power management.                                                           |

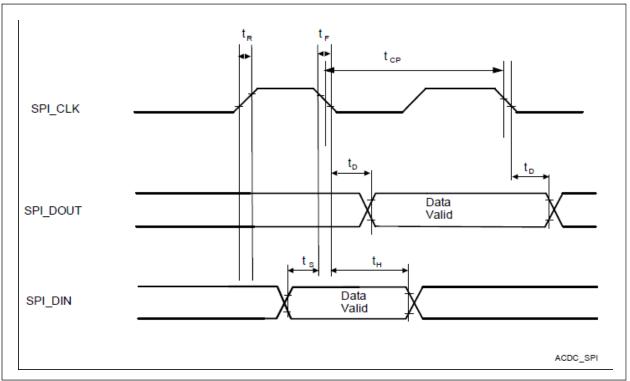

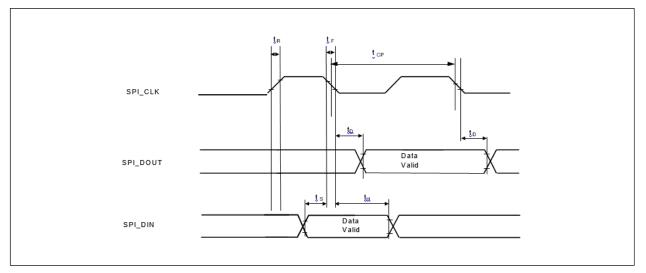

# 2.4 Management and SPI Flash Interfaces

#### Table 2-5.Management Interfaces

| Pin #     | Pin Name              | Pin Type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|-----------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MBus Inte | rface                 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4         | ULP_WAKE_N            | I/O      | ULP Wake.<br>This pin is used by the external Management Controller (CSME) to wake the device from ULP.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 11        | SMB_CLK               | 1/0      | SMBus Clock.         Must connect to PCH's SML0_CLK pin.         One clock pulse is generated for each data bit transferred.         Pull this signal up to 3.3 Vdc (auxiliary supply) through a 499 Ω resistor to support 1 MHz (while in Sx mode).         The resistor value might be adjusted to a higher value to meet the VOH and VOL voltage.                                                                                                                                                                                         |

| 10        | SMB_DATA              | 1/0      | level requirements. Refer to the I225/I226 Design Checklist for more detail.         SMBus Data.         Connect to PCH's SML0_DAT channel.         Stable during the high period of the clock (unless it is a start or stop condition).         Pull this signal up to 3.3 Vdc (auxiliary supply) through a 499 Ω resistor to support 1 MHz (while in Sx mode).         The resistor value might be adjusted to a higher value to meet the VOH and VOL voltage-level requirements. Refer to the I225/I226 Design Checklist for more detail. |

| PI Master | Interface             |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 34        | SPI_DOUT/<br>SEC_ENA  | 0        | SPI Data Output.<br>This pin is also SPI Flash Security strapping. During normal operation, this pin should be connected to an external 10 K $\Omega$ pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                      |

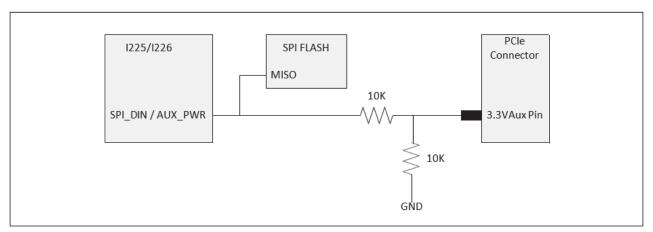

| 36        | SPI_DIN/AUX_PWR       | 1        | Holding Low on this pin will not disable Firmware Authentication (Contend ID # <u>632906).</u> SPI Data Input.         This pin is also the AUX_PWR strapping. An external 10 KΩ pull-up resistor is required in systems on which the device gets power during D3cold. In Network Interface Card (NIC) designs this pin should be connected as shown in Figure 2-2.                                                                                                                                                                          |

| 35        | SPI_CLK               | 0        | SPI Clock.<br>During normal operation, this pin should be connected to an external 10 KΩ pull- down resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 37        | SPI_CS_N/<br>PCIE_ENA | 0        | SPI Chip Select. Active low signal. During normal operation, this pin should be connected to an external 10 K $\Omega$ pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                     |

#### Figure 2-2. AUX\_PWR Strapping Connection

# 2.5 LED / JTAG / UART Interface

# Table 2-6.LED/UART/JTAG Interface

| Pin # | Pin Name                   | Pin Type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|----------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32    | LED0                       | 0        | LEDO.<br>This signal is used for the programmable LED.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 31    | LED1                       | 0        | LED1.<br>This signal is used for the programmable LED.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 30    | LED2                       | 0        | LED2.<br>This signal is used for the programmable LED.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 29    | JTAG_CLK                   | 1        | JTAG Test Clock.<br>The signals TDI, TDO and TMS are synchronous subject to this JTAG test clock.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16    | JTAG_RSTN                  | 1        | JTAG Test Reset.<br>At low, the JTAG is in the reset state and the multiplexed pins JTAG/SDPs act as SDPs. This<br>pin has an internal weak pull-down that holds the JTAG controller in its reset state if the pin<br>is left open.                                                                                                                                                                                                                                                                                       |

| 17    | JTAG_TMS_SDP2              |          | JTAG Test Mode Select. Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 18    | JTAG_TDO/<br>MDI_LANE_SWAP | O / Prg  | JTAG Serial Test Data Output. MDI<br>Lane Swap Configuration.<br>This pin is also for the MDI lane swap strapping pin. It has an internal weak pull- up resistor<br>and should be connected to an external 10 KΩ resistor if needed to be sampled at a low level.<br>At a high level, all MDI lanes are default. MDI pins are shown in Figure 2-1.<br>At a low level (when strapped), all MDI lanes are swapped. Refer to the <i>I225/I226 Lane Swap</i><br><i>Configuration and Reference Schematic</i> for more detail. |

| 19    | JTAG_TDI_SDP1              | I        | JTAG Serial Test Data Input. Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# 2.6 Miscellaneous Signals

#### Table 2-7. Miscellaneous Signals

| Pin # | Pin Name      | Pin Type | Function                                                                                                                                                         |

|-------|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 41    | XTAL_IN       | AI       | Crystal — Oscillator Input. –<br>A crystal must be connected between XTAL1 and XTAL2. Additional load<br>capacitances must also tie both pins to ground.         |

| 40    | XTAL_OUT      | AO       | Crystal — Oscillator Output<br>A crystal must be connected between XTAL1 and XTAL2. Additional load<br>capacitances must also tie both pins to ground.           |

| 15    | SDPO          | Prg      | Software Defined Pin 0 (SDP0).<br>This pin can be selected as input or output mode.                                                                              |

| 1     | LAN_PWR_GOOD  | 1        | LAN Power Good<br>A 3.3 Vdc input signal. A transition from low-to-high initializes the I225/I226 into<br>operation.                                             |

| 2     | LAN_DISABLE_N | 1        | LAN Disable Input.<br>This is a 3.3 Vdc input signal for D3Cold support only.<br><i>Note:</i> This pin is asynchronous.                                          |

| 5, 6  | VDD_CTRL      | AO       | Internal SVR control pin (SVR switching Node). Connect to a 1.0 $\mu H$ inductor and capacitors to provide a 0.95V rail with a worst-case tolerance $\pm 10\%$ . |

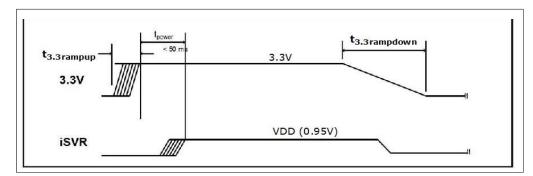

# 2.7 Power Supply

#### Table 2-8.Power Supply

| Pin #            | Pin Name   | Pin Type | Function                                                                                                                                                                                                                      |

|------------------|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |            |          | DCDC Power Supply.                                                                                                                                                                                                            |

| 7                | +3.3V_DC   | PWR      | This supply must provide a nominal voltage of 3.3 Vdc with a worst-case tolerance ±10%.                                                                                                                                       |

|                  |            |          | Pad-Voltage Domain Supply.                                                                                                                                                                                                    |

| 1/ 33            | +3 3// PAD | PWR      | This supply must provide a nominal voltage of 3.3 Vdc with a worst-case tolerance $\pm 10\%$ at the corners, respectively.                                                                                                    |

| 14, 33 +3.3V_PAD |            | FWK      | <i>Note:</i> Short cutting this voltage domain with others of same nominal value is not allowed on the I225/I226. For optimal power-consumption figure of merits, the lowest possible voltage must be selected in the system. |

|                  |            |          | PCIe High-Voltage Domain Supply.                                                                                                                                                                                              |

| 23               | +3.3V_VPH  | PWR      | This supply must provide a nominal voltage of 3.3 Vdc with a worst-case tolerance ±10%.                                                                                                                                       |

|                  |            |          | XO Pad-Voltage Domain P Supply.                                                                                                                                                                                               |

| 39               | +3.3V_XO   | PWR      | This supply must provide a nominal voltage of 3.3 Vdc with a worst-case tolerance ±10%.                                                                                                                                       |

| 43               |            | PWR      | CDB High-Voltage Domain Supply.                                                                                                                                                                                               |

| 45               | +3.3V_CDB  | PWK      | This supply must provide a nominal voltage of 3.3 Vdc ±10%.                                                                                                                                                                   |

|                  |            |          | High-Voltage Domain Supply.                                                                                                                                                                                                   |

| 47, 53           | +3V3_A     | PWR      | This is the group of supply pins for the high voltage domain. It supplies the AFE of the GbE PHY. This supply must provide a nominal voltage of 3.3 Vdc with a worst-case tolerance $\pm 10\%$ at the corners, respectively.  |

|                  |            |          | PCIe Low-Voltage Domain Supply.                                                                                                                                                                                               |

| 26               | VDD_VP     | PWR      | This supply must provide a nominal voltage of 0.95 Vdc with a worst-case tolerance $\pm 10\%$ .                                                                                                                               |

### Table 2-8.Power Supply

| Pin #            | Pin Name   | Pin Type | Function                                                                                                                                                                                                                 |

|------------------|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |            |          | Core-Voltage Domain Supply.                                                                                                                                                                                              |

| 9, 38            | VDD_CORE   | PWR      | This supply must provide a nominal voltage of 0.95 Vdc with a worst-case tolerance $\pm 10\%$ .                                                                                                                          |

|                  |            |          | Low-Voltage Domain Supply.                                                                                                                                                                                               |

| 44, 50, 56 VDD_A |            | PWR      | This is the group of supply pins for the low voltage domain. It supplies mixed signal blocks in the AFE and CDB of the GbE PHY. This supply must provide a nominal voltage of 0.95 Vdc with a worst-case tolerance ±10%. |

| 8                | Reserved   | PWR      | Fusing Domain Supply.                                                                                                                                                                                                    |

| 0                | 8 Reserved |          | During normal operation this pin should be tied to ground.                                                                                                                                                               |

|                  |            |          | General Device Ground.                                                                                                                                                                                                   |

| EPAD             | EPAD       | GND      | The EPAD* is the exposed pad at the bottom of the package. This pad must be properly connected to the ground plane of the Printed Circuit Board (PCB).                                                                   |

# 2.7.1 Leakage Avoidance on LAN Power Disconnect

When the I225/I226 is completely powered down using a FET to cut off the +3.3V\_LAN power supply, there might be leakage on these five pins:

- Pin 3 PE\_CLKREQ\_N

- Pin 4 ULP\_WAKE\_N

- Pin 10 SMB\_DATA

- Pin 11 SMB\_CLK

- Pin 12 PE\_WAKE\_N

To avoid leakage, a basic logic MOSFET can be setup to prevent the leakage path. Refer to the I225/I226 Design Checklist for more detail.

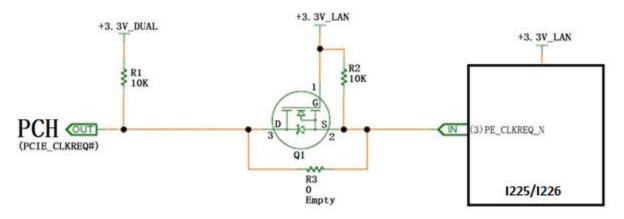

Figure 2-3. Leakage Protection Circuit

# 3.0 Interconnects

#### 3.1 PCIe Interface

The I225/I226 is connected to the platform when the system is at its active state by a one lane PCIe gen 2 (5.0 GT/s) version 3.1 interface. This interface includes the following signals:

- Serial differential pair running at 5 Gb/s for Rx RX0 pair.

- Serial differential pair running at 5 Gb/s for Tx TX0 pair.

- 100 MHz differential clock input PE\_CLK pair.

- Power and clock good indication PE\_RSTn.

- Clock control signal CLKREQn.

- System wakeup signal PE\_WAKEn

### 3.2 Non-Volatile Memory (NVM) Flash

#### 3.2.1 General Overview

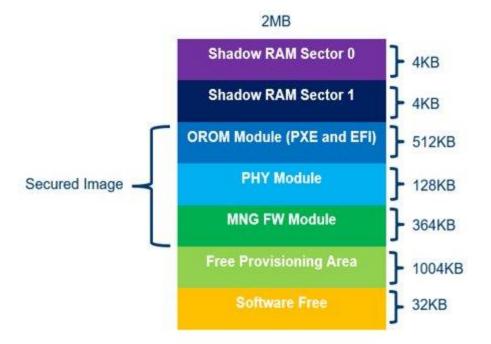

The I225/I226 uses a Flash device for storing product configuration information. The Flash is consist of several blocks listed in the sections that follow, summarized in Table 3-1 and shown in Figure 3-1. More granular modules in the NVM are listed in Table 3-1. The various blocks and its programming method are detailed in the following sections. For its operation the I225/I226 requires a 1 MB Flash as a minimum and a 2 MB Flash if OROM is needed.

- Legacy EEPROM Hardware accessed modules (Block 0 and Block 1) Loaded by the I225/I226 hardware after power-up, PCI reset de-assertion, D3 to D0 transition, or software reset. Different hardware sections in the Flash are loaded at different events. The hardware block is loaded to a shadow RAM in the device. It is located at the first 2 x 4 KB sectors in the Flash.

- Secured Image (Block 2) The following data sections are protected by an RSA signature:

- CSS Header The CSS header describes the modules within the protected block and includes the security signature of the block. The CSS header is counted as part of the firmwaremodule for the sake of its size in the NVM.

- Firmware Module The firmware module contains the code for the embedded controller, a list of supported Flash devices and a RO update section. The firmware module is loaded at power up and firmware reset.

- PHY Module The PHY code is loaded by the PHY cluster for its functionality following a power up or any

reset that affect the PHY.

- Expansion/Option ROM Module (OROM Module) This block is optional and might exist only on larger Flash sizes than 1 MB. It holds code that is expected to be executed by the system at pre-operating system state. The option ROM module might include the following sub-modules: PXE driver, iSCSI boot image, UEFI network driver and can also include a CLP module.

- Free Provisioning Module (Block 3) This block is used by software to program a new secured image.

- mDNS Records A / B (Block3 / Block 4) The mDNS records are used by the CSME firmware for mDNS offload proxy while the system is in D3. It is software's responsibility to program these records before entering the D3 state. The mDNS records are expected to reside adjacent to the firmware space. So, the mDNS records are stored in the A space or B space (as shown in Figure3-1) depending in the location of the secured image.

- Software Free Access Module (Block 4) This module is used mainly by software. It also contains the mDNS records used by the Manageability Engine (ME) firmware for mDNS offload proxy while the system is in D3. Note that the structure of this block is outside the scope of this document.

| Module Name             | Module Size       | Module Pointer Location                              |  |

|-------------------------|-------------------|------------------------------------------------------|--|

| Shadow RAM Sector 0     | 4 KB              | Module starts at absolute address 0 in the Flash.    |  |

| Shadow RAM Sector 1     | 4 KB              | Module starts at absolute address 4 KB in the Flash. |  |

| CSS Header              | inc. in FW Module | Word offset 0x10 in the shadow RAM.                  |  |

| Firmware Module         | 364 KB            | The address is defined in the CSS header.            |  |

| PHY Module              | 128 KB            | Word offset 0x7F0 in the shadow RAM.                 |  |

| OROM Module             | 512 KB            | Offset 0x4A in the shadow RAM.                       |  |

| Free Provisioning Space | 1004 KB           | Offset 0x40 in the shadow RAM.                       |  |

| Software Free           | 16 KB             | Word offset 0x7F1 in the shadow RAM.                 |  |

| mDNS Records            | 16 KB             | Offset 0x25 in the shadow RAM.                       |  |

| Table 3-1 | . NVM | Modules   |

|-----------|-------|-----------|

|           |       | 1 IOuutes |

All previous pointers are 16-bit words. The most significant bit of these pointers is set to 1b stating that the pointers define an absolute address outside the shadow RAM space. The other 15 least significant bits of these pointers specify an address defined in 4 KB units.

#### Figure 3-1. NVM Structure

*Note:* This document uses the terms NVM and Flash to refer to the non-volatile memory used by the I225/I226. both terms have the same meaning.

### 3.2.2 NVM Security

The NVM update is protected by secured integrity check. It ensures that only an Intel approved image can be updated on I225/I226 devices after manufacturing. The updated image is checked against a digital SHA256 signature that is then encrypted by a private 2048-bit RSA Intel key. The modules that are protected by the secured integrity check are:

- Optional OROM module

- PHY module

- Firmware module

Any updated image includes all these secured modules.

## 3.2.3 Shadow RAM

The I225/I226 maintains the first two 4 KB sectors, Sector 0 and Sector 1 (block 0 and block 1), for the hardware configuration content. At least one of these two sectors must be valid at any given time or else the I225/I226 is set by hardware default. Following a Power On Reset (POR), the I225/I226 copies the valid lower 4 KB sector of the Flash device into an internal shadow RAM. Any further accesses of the software or firmware to this section of the NVM are directed to the internal shadow RAM. After a software command, modifications made to the shadow RAM content are then copied by the I225/I226 manageability into the other 4 KB sector of the NVM, flipping circularly the valid sector between sector 0 and 1 of NVM.

This mechanism provides the following advantages:

- 1. A seamless backward compatible read/write interface for software/firmware to the first 4 KB of the NVM as if an external EEPROM device was connected. This interface is referred as EEPROM-mode access to the Flash.

- 2. A way for software to protect image-update procedure from power down events by establishing a doubleimage policy. It relies on having pointers to all the other NVM modules mapped in theNVM sector that is mirrored in the internal shadow RAM.

- 3. A way to ensure that a hardware auto-load event, which occurs further to a PCIe reset event, can be completed within the PCIe timing constraints (100 ms) even if the Flash is occupied performing an erase operation initiated just before the reset.

Due to NVM security reasons, hardware does not allow any Flash accesses until the NVM is authenticated and the Flash blocks are identified by the device.

### 3.2.4 Protected Areas and Words

The I225/I226 provides a mechanism to protect against programming (write access) specific areas in the Flash as follows:

- The two shadow RAM sectors (the first 8 KB of the Flash device) are write protected. During normal operation, this area is programmed only by the device (autonomously) following a request from the software updating the shadow RAM.

- The secured block containing the CSS header, firmware content, PHY cluster content and the OROM module is also write protected. Updating the secured block, software can program the free provisioning area and request the device to make it the next valid secured block. Once it is authenticated by the device, it becomes the valid secured block and then it is write protected.

The following table lists the protected words in the shadow RAM space.

#### Table 3-3. Protected Words List

| Word Offset | Word Name                                     | Word Offset | Word Name                                                         |

|-------------|-----------------------------------------------|-------------|-------------------------------------------------------------------|

| 0x000x02    | Ethernet Individual MAC Address               | 0x2D        | Start of RO Area                                                  |

| 0x03        | Compatibility Bytes                           | 0x2F        | VPD Pointer                                                       |

| 0x08        | PBA Number 0                                  | 0x34        | PCIe PHY Configuration 0 Low                                      |

| 0x09        | PBA Number 1                                  | 0x35        | PCIe PHY Configuration 0 High                                     |

| 0x0D        | Device ID                                     | 0x37        | Alternate MAC Address Location                                    |

| 0x0E        | Vendor ID                                     | 0x38        | PCIe PHY Configuration 1 Low                                      |

| 0x0A        | VPD Enable Flag                               | 0x39        | PCIe PHY Configuration 1 High                                     |

| 0x10        | Secure Area Start Address                     | 0x3A        | PCIe PHY Configuration 2 low/Reset to PCIe<br>PHY Delay (0x40 μs) |

| 0x11        | Flash Device Size                             | 0x3C        | PXE VLAN Pointer                                                  |

| 0x12        | EEPROM Sizing and Protected Fields            | 0x3D        | iSCSI Boot Configuration Pointer                                  |

| 0x17        | Software Reset CSR Auto Configuration Pointer | 0x40        | Free Provisioning Area Pointer                                    |

| 0x22        | LAN Power Consumption                         | 0x41        | Free Provisioning Area Size                                       |

| 0x23        | PCIe Reset CSR Auto Configuration Pointer     | 0x44        | PCIe L1 Sub-states Capability Low                                 |

| 0x24        | Initialization Control 3                      | 0x45        | PCIe L1 Sub-states Capability High                                |

| 0x25        | mDNS Records Area Offset                      | 0x46        | PCIe L1 Sub-states Control First Low                              |

| 0x26        | mDNS Records Area Size                        | 0x47        | PCIe L2 Sub-states Control First High                             |

| 0x27        | CSR Auto Configuration Power-up Pointer       | 0x48        | PCIe L2 Sub-states Control Second                                 |

| 0x28        | PCIe Control 2                                | 0x4A        | EXP.ROM Boot Code Section Pointer                                 |

| 0x2A        | CDQM Memory Base Low                          | 0x50        | RO Commands Version                                               |

| 0x2B        | CDQM Memory Base High                         | 0x51        | Firmware Module Configuration Pointer                             |

| 0x2C        | End of Read-only (RO) Area                    |             |                                                                   |

#### 3.3 Network Interfaces

#### 3.3.1 Overview

The I225/I226 provide a complete CSMA/CD function with an integrated MAC and PHY. It supports the following link speeds: 10 Mb/s; 100 Mb/s; 1000 Mb/s and 2.5 Gb/s. Full Duplex is supported at all link speed while Half Duplex is supported at 10 Mb/s; 100 Mb/s only.

# 3.4 Configurable LED Outputs

The I225/I226 provides three LEDs / GPIO pins that can be used to indicate different speed status of the link. The default setup of the LEDs is loaded from the NVM word offsets 0x1C and 0x1F. This setup is reflected in the LEDCTL register. The software device driver can change this setup accessing the LEDCTL register. For each of the LEDs, the following parameters can be defined:

- LED Functionality (Mode): Defines which information is reflected by this LED as listed in Table3-4.

- Polarity (IVRT): Defines the polarity of the LED.

- Blink mode (BLINK): Determines whether or not the LED should blink or be stable. In addition, the blink rate of all LEDs can be defined by the *Global Blink Mode* flag in the LEDCTL register. The possible rates are 200 ms or 83 ms for each phase. There is one rate for all the LEDs.

| LEDx_MODE (x=03)            | LED Functionality                                                                                                                                                                                               |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0                         | LED_ON - Always high (Asserted)                                                                                                                                                                                 |

| 0x1                         | LED_OFF - Always low (De-asserted)                                                                                                                                                                              |

| 0x2                         | LINK_UP - Asserted when any speed link is established                                                                                                                                                           |

| 0x3                         | FILTER_ACTIVITY - Asserted when link is established and packets are being transmitted or received that passed MAC filtering                                                                                     |

| 0x4                         | LINK_ACTIVITY - Asserted when link is established and when there is no transmit or receive activity. When BLINK is set, the LED is on if there is link and it blinks for activity (either receive or transmit). |

| 0x5                         | LINK_10 - Asserted when a 10 Mb/s link is established                                                                                                                                                           |

| 0x6                         | LINK_100 - Asserted when a 100 Mb/s link is established                                                                                                                                                         |

| 0x7                         | LINK_1000 - Asserted when a 1000 Mb/s link is established                                                                                                                                                       |

| 0x8                         | LINK_2500 - Asserted when a 2500 Mb/s link is established                                                                                                                                                       |

| 0x9                         | SDP_MODE - The SDP pin functions as an SDP. SDP02 on LED 02 pins respectively.                                                                                                                                  |

| 0xA                         | PAUSED - Asserted when the transmitter is PAUSED by the flow scheme                                                                                                                                             |

| OxB                         | ACTIVITY - Asserted when link is established and packets are being transmitted or received                                                                                                                      |

| 0xC                         | LINK_10/100 - Asserted when either 10 or 100 Mb/s link is established                                                                                                                                           |

| 0xD                         | LINK_100/1000 - Asserted when either 100 or 1000 Mb/s link is established and maintained                                                                                                                        |

| 0xE                         | LINK_1000/2500 - Asserted when either 1000 or 2500 Mb/s link is established                                                                                                                                     |

| OxF                         | LINK_100/2500 - Asserted when either 100 or 2500 Mb/s link is established and maintained                                                                                                                        |

| The dynamic LED modes (FILT | ER_ACTIVITY, LINK/ACTIVITY, ACTIVITY, PAUSED) should be used with LED Blink mode enabled.                                                                                                                       |

#### Table 3-4. Link Mode Encoding

# 3.5 Transmission of PAUSE Frames

The I225/I226 generates PAUSE packets to ensure there is enough space in its receive packet buffers to avoid packet drop. The I225/I226 monitors the fullness of its receive packet buffers and compares it with the contents of a programmable threshold. When the threshold is reached, the I225/I226 sends a PAUSE frame. The I225/I226 supports the sending of link Flow Control (FC).

### 3.5.1 Operation and Rules

Transmission of link PAUSE frames is enabled by software writing a 1b to the *TFCE* bit in the Device Control register.

The I225/I226 sends a PAUSE frame when Rx packet buffer is full above the high threshold defined in the Flow Control Receive Threshold High (*FCRTHO.RTH*) register field. When the threshold is reached, the I225/I226 sends a PAUSE frame with its pause time field equal to *FCTTV*. The threshold should be large enough to overcome the worst case latency from the time that crossing the threshold is sensed until packets are not received from the link partner. The Flow Control Receive Threshold High value should be calculated as follows:

Flow Control Receive Threshold High = Internal Rx Buffer Size - (Threshold Cross to XOFF Transmission + Round-trip Latency + XOFF Reception to Link Partner response)

Parameter values to be used for calculating the FCRTH0.RTH value are listed in Table 3-5.

#### 3.5.2 Software Initiated PAUSE Frame Transmission

The I225/I226 has the added capability to transmit an XOFF frame via software. This is accomplished by software writing a 1b to the *SWXOFF* bit of the Transmit Control register. Once this bit is set, hardware initiates the transmission of a PAUSE frame in a manner similar to that automatically generated by hardware.

The SWXOFF bit is self-clearing after the PAUSE frame has been transmitted.

*Note:* The Flow Control Refresh Threshold mechanism does not work in the case of software- initiated flow control. Therefore, it is the software's responsibility to re-generate PAUSE frames before expiration of the pause counter at the other partner's end.

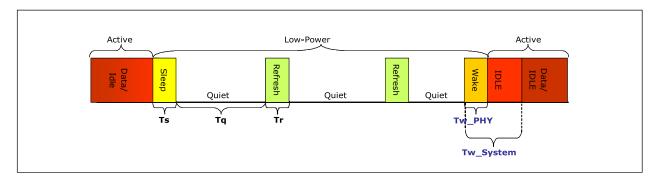

## 3.6 Energy Efficient Ethernet (EEE)

Energy Efficient Ethernet (EEE) Low Power Idle (LPI) mode defined in IEEE802.3az optionally enables power saving by switching off part of the LAN device functionality when no data needs to be transmitted or/ and received. The decision as to whether or not the LAN device transmit path should enter LPI mode or exit LPI mode is done according to transmit needs. Information as to whether or not a link partner has entered LPI mode is detected by the LAN device and is used for power saving in the receive circuitry.

I225 doesn't support EEE, but I226 does support EEE

When no data needs to be transmitted, a request to enter transmit LPI is issued on the internal xxMII Tx interface causing the PHY to transmit sleep symbols for a pre-defined period of time followed by a quiet period. During LPI, the PHY periodically transmits refresh symbols that are used by the link partner to update adaptive filters and timing circuits in order to maintain link integrity. This quiet- refresh cycle continues until transmitting normal interframe encoding on the internal xxMII interface. The PHY communicates to the link partner the move to active link state by sending wake symbols for a pre-defined period of time. The PHY then enters a normal operating state where data or idle symbols are transmitted.

In the receive direction, entering LPI mode is triggered by receiving sleep symbols from the link partner. This signals that the link partner is about to enter LPI mode. After sending the sleep symbols, the link partner ceases transmission. When a link partner enters LPI, the PHY indicates assert low power idle on the internal xxMII RX interface and the LAN device's receiver disables certain functionality to reduce power consumption.

Figure 3-2 shows, and Table 3-6 lists the general principles of EEE LPI operation on the Ethernet Link.

#### Figure 3-2. Energy Efficient Ethernet Operation

#### Table 3-6. Energy Efficient Ethernet Parameters

| Parameter                                   | Description                                                                                              |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Sleep Time (Ts)                             | Duration PHY sends sleep symbols before going quiet.                                                     |

| Quiet Duration (Tq)                         | Duration PHY remains quiet before it must wake for refresh period.                                       |

| Refresh Duration (Tr)                       | Duration PHY sends refresh symbols for timing recovery and coefficient synchronization.                  |

| PHY Wake Time (Tw_PHY)                      | Minimum duration PHY takes to resume to an active state after decision to wake.                          |

| Receive System Wake Time<br>(Tw_System_rx)  | Wait period where no data is expected to be received to give the local receiving system time to wake up. |

| Transmit System Wake Time<br>(Tw_System_tx) | Wait period where no data is transmitted to give the remote receiving system time to wake up.            |

### 3.6.1 EEE Auto-Negotiation

Auto-negotiation provides the capability to negotiate EEE capabilities with the link partner using the next page mechanism defined in IEEE802.3 Annex 28C. IEEE802.3 auto-negotiation is performed at power up, on command from software, upon detection of a PHY error or following linkre-connection.

During the link establishment process, both link partners indicate their EEE capabilities via the IEEE802.3 autonegotiation process. If EEE is supported by both link partners for the negotiated PHY type, then the EEE function can be used independently in either direction.

The I226 supports EEE auto-negotiation. EEE capabilities advertised during auto-negotiation can be modified via the *EEEEEE\_2\_5G\_AN, EEE\_1G\_AN* and *EEE\_100M\_AN* flags in the IPCNFG register.

# 4.0 **Power Management and Power Consumption**

#### 4.1 Power Management

The I225/I226 supports an intelligent power management scheme. The three global power states are as follows:

- When the system is at its functional state it auto-negotiates the link speed to the highestcommon denominator for best performance.

- When the system is at its low power state, the I225/I226 can be configured to auto-negotiate the link to lower speeds, saving system power.

- The I226 can be put into an Ultra-Low Power (ULP) state when the link is disconnected.

- Platform hardware needs to connect I226's LAN\_DISABLE\_N pin to a GPIO at either platform or EC.

- System BIOS will need to implement the \_On/\_Off method on the GPIO pin.

- Enable ULP entry on D3Cold entry: the \_On method should de-assert (drive HIGH) GPIO connected to LAN\_DISABLE\_N.

- Exit ULP on D3Cold exit: \_Off method should assert (drive LOW) LAN\_DISABLE\_N.

- There are three ways to exit ULP:

- ULP by the user Cable detected event (user plugs in the LAN cable).

- ULP by the host On exit from RTD3, the operating system calls the BIOS \_ON method that can be assigned to de-assert the LAN\_DISBALE\_N pin using GPIO. This event causes ULP to exit.

- ULP by CSME The CSME can trigger a ULP exit by asserting the ULP\_WAKE\_N pin. This can be done by connecting SMB\_DATA to ULP\_WAKE\_N.

#### 4.2 General Power State Information

#### 4.2.1 PCIe Device Power States