# Low Power, 3.0kV rms Dual I<sup>2</sup>C Isolators

#### **FEATURES**

Bidirectional I<sup>2</sup>C communication

Ultra-low power consumption

Supports up to 2MHz operation

Open-drain interfaces

Side 1 outputs with 3.5 mA sink current

Side 2 outputs with 35 mA sink current

3.0V to 5.5V supply/logic levels

3000Vrms for 1 minute per UL 1577 CSA Component Acceptance Notice 5A

DIN VDE V 0884-11:2017-01

V<sub>IORM</sub> = 565V peak

CQC certification per GB4943.1-2011

AEC-Q100 qualification

Wide temperature range: -40°C to 125°C

RoHS-compliant, NB SOIC-8 package

#### **APPLICATIONS**

Isolated I<sup>2</sup>C, SMBus, PMBus interfaces Multilevel I<sup>2</sup>C interfaces Electric and Hybrid-Electric Vehicles Open-Drain Networks I<sup>2</sup>C Level Shifting Power supplies

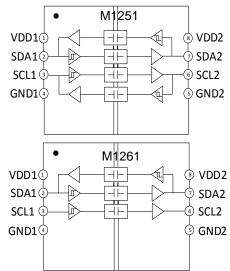

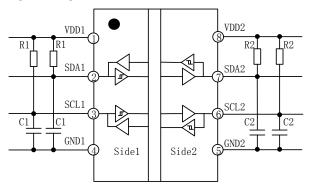

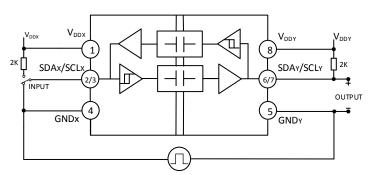

#### **FUNCTIONAL BLOCK DIAGRAMS**

Figure 1. M1251/1261 functional Block Diagram

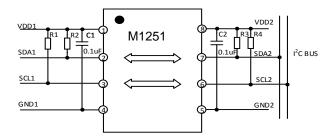

Figure 2. M1251 Typical Application Circuit

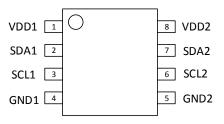

## PIN CONFIGURATIONS AND FUNCTIONS

### M1251/1261 Pin Function Descriptions

| 111201/1201 I in Function Descriptions |      |                                                                 |  |  |  |  |

|----------------------------------------|------|-----------------------------------------------------------------|--|--|--|--|

| Pin No.                                | Name | Description                                                     |  |  |  |  |

| 1                                      | VDD1 | Supply Voltage for Isolator Side 1.                             |  |  |  |  |

| 2                                      | SDA1 | Serial data input / output, side 1.                             |  |  |  |  |

| 3                                      | SCL1 | Serial clock input / output, side 1.                            |  |  |  |  |

| 4                                      | GND1 | Ground 1. This pin is the ground reference for Isolator Side 1. |  |  |  |  |

| 5                                      | GND2 | Ground 2. This pin is the ground reference for Isolator Side 2. |  |  |  |  |

| 6                                      | SCL2 | Serial clock input / output, side 2.                            |  |  |  |  |

| 7                                      | SDA2 | Serial data input / output, side 2.                             |  |  |  |  |

| 8                                      | VDD2 | Supply Voltage for Isolator Side 2.                             |  |  |  |  |

Figure 3. M1251/1261 Pin Configuration

## **ABSOLUTE MAXIMUM RATINGS**

Table 1. Absolute Maximum Ratings<sup>1,2</sup>

| Parameter                                                                                  | Rating                             |

|--------------------------------------------------------------------------------------------|------------------------------------|

| Supply Voltages (V <sub>DD1</sub> -GND <sub>1</sub> , V <sub>DD2</sub> -GND <sub>2</sub> ) | -0.5 V to +7.0 V                   |

| Signal Voltage SDA1/SCL1                                                                   | -0.5 V to V <sub>DDx</sub> + 0.5 V |

| Signal Voltage SDA2/SCL2                                                                   | -0.5 V to V <sub>DDx</sub> + 0.5 V |

| Average Output Current SDA1/SCL1 (I <sub>O1</sub> )                                        | -20 mA to +20 mA                   |

| Average Output Current SDA2/SCL2 (I <sub>O2</sub> )                                        | -100 mA to +100 mA                 |

| Storage Temperature (T <sub>ST</sub> ) Range                                               | -55°C to +150°C                    |

| Maximum junction temperature T <sub>J</sub> (MAX)                                          | +150°C                             |

#### Notes:

## RECOMMENDED OPERATING CONDITIONS

**Table 2. Recommended Operating Conditions**

| Parameter                                                                                                    | Symbol                        | Min           | Тур | Max                   | Unit |

|--------------------------------------------------------------------------------------------------------------|-------------------------------|---------------|-----|-----------------------|------|

| Supply Voltage                                                                                               | V <sub>DDx</sub> <sup>1</sup> | 3             |     | 5.5                   | V    |

| Input/Output Signal Voltage (V <sub>SDA1</sub> , V <sub>SCL1</sub> , V <sub>SDA2</sub> , V <sub>SCL2</sub> ) |                               | 0             |     | $V_{DDx}^{1}$         | V    |

| Low-level input voltage, side 1                                                                              | VIL1                          | 0             |     | 0.47                  | V    |

| High-level input voltage, side 1                                                                             | VIH1                          | $0.7*V_{DD1}$ |     | $V_{DD1}$             | V    |

| Low-level input voltage, side 2                                                                              | VIL2                          | 0             |     | $0.3^*V_{\text{DD2}}$ | V    |

| High-level input voltage, side 2                                                                             | VIH2                          | $0.7*V_{DD2}$ |     | $V_{\text{DD2}}$      | V    |

| Output current, side 1                                                                                       | I <sub>OL1</sub>              | 0.5           |     | 3.5                   | mA   |

| Output current, side 2                                                                                       | I <sub>OL2</sub>              | 0.5           |     | 35                    | mA   |

| Capacitive load, side 1                                                                                      | C1                            |               |     | 40                    | pF   |

| Capacitive load, side 2                                                                                      | C2                            |               |     | 400                   | pF   |

| Operating frequency                                                                                          | fmax                          |               |     | 2                     | MHz  |

| Ambient Operating Temperature                                                                                | T <sub>A</sub>                | -40           |     | 125                   | °C   |

#### Notes:

<sup>&</sup>lt;sup>1</sup> All voltage values here within are with respect to the local ground pin (GND1 or GND2) and are peak voltage values.

<sup>&</sup>lt;sup>2</sup> Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

$<sup>^{1}</sup>$  V<sub>DDx</sub> is the side voltage power supply V<sub>DD</sub>, where x = 1 or 2.

#### **Truth Tables**

### Table 3. M1251/1261 Truth Table

| V <sub>Ix</sub> Input <sup>1</sup> | V <sub>DDI</sub> State <sup>1</sup> | V <sub>DDO</sub> State <sup>1</sup> | Vox Output <sup>1</sup> |

|------------------------------------|-------------------------------------|-------------------------------------|-------------------------|

| Low                                | Powered <sup>2</sup>                | Powered <sup>2</sup>                | Low                     |

| High                               | Powered <sup>2</sup>                | Powered <sup>2</sup>                | High Impedance          |

| Open <sup>4</sup>                  | Powered <sup>2</sup>                | Powered <sup>2</sup>                | High Impedance          |

| Don't Care                         | Unpowered <sup>3</sup>              | Powered <sup>2</sup>                | High Impedance          |

| Don't Care                         | Powered <sup>2</sup>                | Unpowered <sup>3</sup>              | High Impedance          |

#### Notes

## **SPECIFICATIONS**

### **ELECTRICAL CHARACTERISTICS**

#### Table 4. DC Specifications

$V_{DD1} - V_{GND1} = V_{DD2} - V_{GND2} = 3.3 V_{DC} \pm 10\% \ or \ 5 V_{DC} \pm 10\%, \ T_A = 25 ^{\circ}C, \ unless \ otherwise \ noted.$

| Parameter                                                                                       | Symbol               | Min                    | Тур            | Max                   | Unit | Test Conditions/Comments                                          |

|-------------------------------------------------------------------------------------------------|----------------------|------------------------|----------------|-----------------------|------|-------------------------------------------------------------------|

| SIDE 1 LOGIC LEVELS                                                                             |                      |                        |                |                       |      |                                                                   |

| Voltage input threshold low, SDA1 and SCL1                                                      | VILT1                | 470                    | 510            | 570                   | mV   |                                                                   |

| Voltage input threshold high, SDA1 and SCL1                                                     | $V_{IHT1}$           | 540                    | 580            | 630                   | mV   |                                                                   |

| Voltage input hysteresis                                                                        | $V_{HYST1}$          | 50                     | 70             |                       | mV   | VIHT1 –VILT1                                                      |

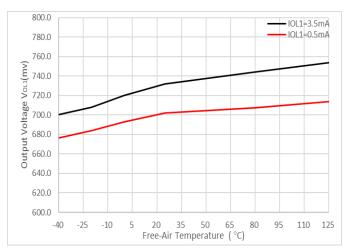

| Low-level output voltage, SDA1 and SCL1                                                         | $V_{OL1}$            | 650                    | 720            | 800                   | mV   | 0.5 mA ≤ (IsDA1 and IscL1) ≤ 3.5 mA                               |

| Low-level output voltage to high-<br>level input voltage threshold<br>difference, SDA1 and SCL1 | ΔVοιτ1 <sup>1</sup>  | 60                     | 120            |                       | mV   | 0.5 mA ≤ (ISDA1 and ISCL1) ≤ 3.5 mA                               |

| SIDE 2 LOGIC LEVELS                                                                             |                      |                        |                |                       |      |                                                                   |

| Voltage input threshold low, SDA2 and SCL2                                                      | VILT2                | 0.30* V <sub>DD2</sub> |                | 0.42*V <sub>DD2</sub> | ٧    |                                                                   |

| Voltage input threshold high, SDA2and SCL2                                                      | $V_{IHT2}$           | 0.58* V <sub>DD2</sub> |                | 0.69*V <sub>DD2</sub> | V    |                                                                   |

| Voltage input hysteresis                                                                        | VHYST2               | 0.20* V <sub>DD2</sub> | $0.28*V_{DD2}$ |                       | V    | VIHT2 – VILT2                                                     |

| Low-level output voltage, SDA2 and SCL2                                                         | VOL2                 |                        |                | 0.4                   | V    | 0.5 mA ≤ (ISDA2 and ISCL2) ≤ 35 mA                                |

| BOTH SIDES                                                                                      |                      |                        |                |                       |      |                                                                   |

| Input leakage currents, SDA1, SCL1, SDA2, and SCL2                                              | lin                  |                        | 0.01           | 10                    | μΑ   | VSDA1, VSCL1 = V <sub>DD1</sub> ; VSDA2, VSCL2 = V <sub>DD2</sub> |

| V <sub>DDx</sub> <sup>3</sup> Undervoltage Rising<br>Threshold                                  | $V_{DDxUV+}$         | 2.45                   | 2.75           | 2.95                  | ٧    |                                                                   |

| V <sub>DDx</sub> <sup>3</sup> Undervoltage Falling<br>Threshold                                 | V <sub>DDxUV</sub> - | 2.30                   | 2.60           | 2.80                  | V    |                                                                   |

| V <sub>DDx</sub> <sup>3</sup> Hysteresis                                                        | V <sub>DDxUVH</sub>  |                        | 0.15           |                       | ٧    |                                                                   |

Notes

<sup>1</sup> V<sub>Ix</sub>/V<sub>Ox</sub> are the input/output signals of a given channel (SDA or SCL). V<sub>DDI</sub>/V<sub>DDO</sub> are the supply voltages on the input/output signal sides of this given channel.

<sup>&</sup>lt;sup>2</sup> Powered means V<sub>DDx</sub>≥ 2.95 V

$<sup>^{3}</sup>$  Unpowered means  $V_{DDx}$  < 2.30V

$<sup>^4\,\</sup>text{Invalid}$  input condition as an I $^2\text{C}$  system requires that a pullup resistor to  $V_{DD}$  is connected.

<sup>&</sup>lt;sup>1</sup>  $\Delta$  VOIT1 = VOL1 -VIHT1. This is the minimum difference between the output logic low level and the input logic threshold within a given component. This ensures that there is no possibility of the part latching up the bus to which it is connected.

$<sup>^2</sup>$   $V_{\text{DDx}}$  is the side voltage power supply  $V_{\text{DD}},$  where x = 1 or 2.

#### **Table 5. Quiescent Supply Current**

$V_{DD1}$  -  $V_{GND1}$  =  $V_{DD2}$  -  $V_{GND2}$  = 3.3 $V_{DC}$ ±10% or 5 $V_{DC}$ ±10%,  $T_A$ =25°C, R1, R2 = Open; C1, C2 = Open (figure 17), unless otherwise noted. Test method refer to Figure 17.

| Parameter                                           | Symbol               | Min | Тур | Max | Unit | Test Conditions      |  |

|-----------------------------------------------------|----------------------|-----|-----|-----|------|----------------------|--|

|                                                     | IDD1 (Q)             |     | 1.7 | 2.4 | mA   | VSDA1, VSCL1 = GND1; |  |

| M1251 Quiescent Supply Current @ 5VDC               | IDD2 (Q)             |     | 1.4 | 2.1 | mA   | VSDA2, VSCL2 = GND2  |  |

| Supply                                              | IDD1 (Q)             |     | 1.5 | 2.3 | mA   | VSDA1, VSCL1 = VDD1; |  |

|                                                     | IDD2 (Q)             |     | 1.2 | 1.8 | mA   | VSDA2, VSCL2 = VDD2  |  |

|                                                     | Idd1 (Q)             |     | 1.5 | 2.3 | mA   | VSDA1, VSCL1 = GND1; |  |

| M1251 Quiescent Supply Current @ 3.3V <sub>DC</sub> | IDD2 (Q)             |     | 1.2 | 1.8 | mA   | VSDA2, VSCL2 = GND2  |  |

| Supply                                              | IDD1 (Q)             |     | 1.5 | 2.3 | mA   | VSDA1, VSCL1 = VDD1; |  |

|                                                     | I <sub>DD2</sub> (Q) |     | 1.2 | 1.8 | mA   | VSDA2, VSCL2 = VDD2  |  |

|                                                     | IDD1 (Q)             |     | 1.1 | 1.7 | mA   | VSDA1, VSCL1 = GND1; |  |

| M1261 Quiescent Supply Current @ 5V <sub>DC</sub>   | I <sub>DD2</sub> (Q) |     | 1.2 | 1.8 | mA   | VSDA2, VSCL2 = GND2  |  |

| Supply                                              | IDD1 (Q)             |     | 1.2 | 1.8 | mA   | VSDA1, VSCL1 = VDD1; |  |

|                                                     | I <sub>DD2</sub> (Q) |     | 1.2 | 1.8 | mA   | VSDA2, VSCL2 = VDD2  |  |

|                                                     | IDD1 (Q)             |     | 1.0 | 1.5 | mA   | VSDA1, VSCL1 = GND1; |  |

| M1261 Quiescent Supply Current @ 3.3V <sub>DC</sub> | I <sub>DD2</sub> (Q) |     | 1.1 | 1.7 | mA   | VSDA2, VSCL2 = GND2  |  |

| Supply                                              | IDD1 (Q)             |     | 1.1 | 1.7 | mA   | VSDA1, VSCL1 = VDD1; |  |

|                                                     | IDD2 (Q)             |     | 1.1 | 1.7 | mA   | VSDA2, VSCL2 = VDD2  |  |

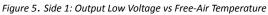

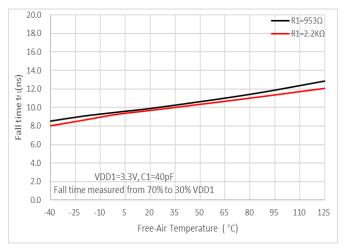

### **Table 6. Switching Specifications**

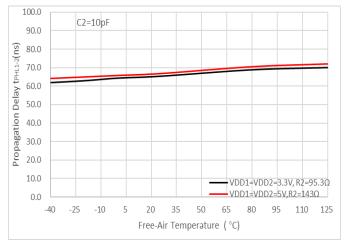

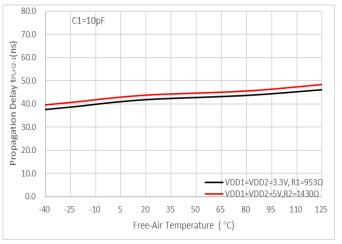

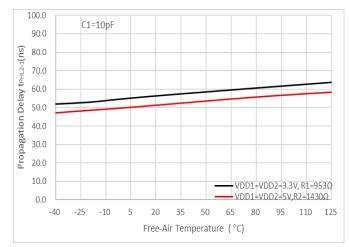

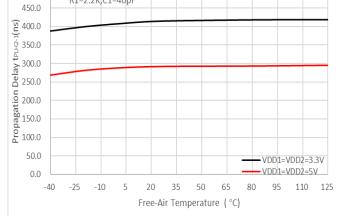

$V_{DD1}$  -  $V_{GND1}$  =  $V_{DD2}$  -  $V_{GND2}$  = 3.3 $V_{DC}$ ±10% or 5 $V_{DC}$ ±10%,  $T_A$ =25°C, unless otherwise noted. Test method refer to Figure 17.

| Parameter                                          | Symbol          | Min | Тур | Max | Unit | Test Conditions/Comments                                                                                    |

|----------------------------------------------------|-----------------|-----|-----|-----|------|-------------------------------------------------------------------------------------------------------------|

| Output Signal Fall Time<br>SDA1, SCL1              | tf1             | 10  | 18  | 30  | ns   | $0.9~V_{DD1}$ to $0.9~V$ ; R1 = 1430 $\Omega$ ,C1 = 40 pF ,@ $5V_{DC}$ supply                               |

|                                                    |                 | 9   | 16  | 28  | ns   | R1 = 953 $\Omega$ , C1 = 40 PF; @ 3.3V <sub>DC</sub> supply                                                 |

|                                                    |                 | 6   | 11  | 18  | ns   | 0.7 $V_{DD1}$ to 0.3 $V_{DD1}$ ; R1 = 1430 $\Omega$ ,C1 = 40 pF ,@ 5 $V_{DC}$ supply                        |

|                                                    |                 | 6   | 10  | 16  | ns   | R1 = 953 $\Omega$ , C1 = 40 PF; @ 3.3V <sub>DC</sub> supply                                                 |

| Output Signal Fall Time (SDA2, SCL2)               | t <sub>f2</sub> | 22  | 36  | 45  | ns   | $0.9V_{DD2}$ to $0.4V$ ; R2 = 143 $\Omega$ , C2 = 400 pF, @ $5V_{DC}$ supply                                |

|                                                    |                 | 20  | 31  | 42  | ns   | R2 = 95.3 $\Omega$ ,C2 = 400 pF; @ 3.3V <sub>DC</sub> supply                                                |

|                                                    |                 | 9   | 16  | 26  | ns   | $0.7 \text{ V}_{DD2}$ to $0.3 \text{ V}_{DD2}$ ; R2 = 143 $\Omega$ , C2 = 400 pF, @ $5\text{V}_{DC}$ supply |

|                                                    |                 | 8   | 14  | 23  | ns   | R2 = 95.3 $\Omega$ ,C2 = 400 pF; @ 3.3V <sub>DC</sub> supply                                                |

| Low-to-High Propagation Delay,<br>Side 1 to Side 2 | tpLH1-2         |     | 45  | 68  | ns   | 0.55 V to 0.7 × $V_{DD2}$ ; R1 = 1430 Ω, R2 = 143 Ω, C1, C2 = 10 pF; @ 5 $V_{DC}$ supply                    |

|                                                    |                 |     | 38  | 57  | ns   | R1 = 953 $\Omega$ , R2 = 95.3 $\Omega$ , C1, C2 = 10 pF; @ 3.3V <sub>DC</sub> supply                        |

| High-to-Low Propagation Delay,<br>Side 1 to Side 2 | tPHL1-2         |     | 67  | 100 | ns   | 0.7 V to 0.4 V; R1 = 1430 $\Omega$ , R2 = 143 $\Omega$ , C1, C2 = 10 pF; @ 5V <sub>DC</sub> supply          |

|                                                    |                 |     | 64  | 96  | ns   | R1 = 953 $\Omega$ , R2 = 95.3 $\Omega$ , C1, C2 = 10 pF; @ 3.3V <sub>DC</sub> supply                        |

| Pulse Width Distortion<br> tpHL1-2 - tpLH1-2       | PWD1-2          |     | 22  | 32  | ns   | R1 = 1430 $\Omega$ , R2 = 143 $\Omega$ , C1, C2 = 10 pF; @ 5V <sub>DC</sub> supply                          |

|                                                    |                 |     | 26  | 39  | ns   | R1 = 953 $\Omega$ , R2 = 95.3 $\Omega$ , C1, C2 = 10 pF; @ 3.3V <sub>DC</sub> supply                        |

| Parameter                                          | Symbol  | Min | Тур | Max | Unit  | Test Conditions/Comments                                                                                                       |

|----------------------------------------------------|---------|-----|-----|-----|-------|--------------------------------------------------------------------------------------------------------------------------------|

| Low-to-High Propagation Delay,<br>Side 2 to Side 1 | tPLH2-1 |     | 44  | 62  | ns    | $0.4 \times V_{DD2}$ to $0.7 \times VDD1$ ; R1 = 1430 $\Omega$ , R2 = 143 $\Omega$ , C1, C2 = 10 pF; @ 5V <sub>DC</sub> supply |

|                                                    |         |     | 42  | 56  | ns    | R1 = 953 $\Omega$ , R2 = 95.3 $\Omega$ , C1, C2 = 10 pF; @ 3.3V <sub>DC</sub> supply                                           |

| High-to-Low Propagation Delay,<br>Side 2 to Side 1 | tPHL2-1 |     | 52  | 78  | ns    | $0.4 \times V_{DD2}$ to $0.9 \text{ V}$ ; R1 = 1430 $\Omega$ , R2 = 143 $\Omega$ , C1, C2 = 10 pF; @ 5V <sub>DC</sub> supply   |

|                                                    |         |     | 57  | 86  | ns    | R1 = 953 $\Omega$ ,R2 = 95.3 $\Omega$ ,C1, C2 = 10 pF; @ 3.3V <sub>DC</sub> supply                                             |

| Pulse Width Distortion<br> tpHL2-1 - tpLH2-1       | PWD2-1  |     | 8   | 16  | ns    | R1 = 1430 $\Omega$ ,R2 = 143 $\Omega$ ,C1,2 = 10 pF; @ 5V <sub>DC</sub> supply                                                 |

|                                                    |         |     | 15  | 30  | ns    | R1 = 953 $\Omega$ ,R2 = 95.3 $\Omega$ ,C1, C2 = 10 pF; @ 3.3V <sub>DC</sub> supply                                             |

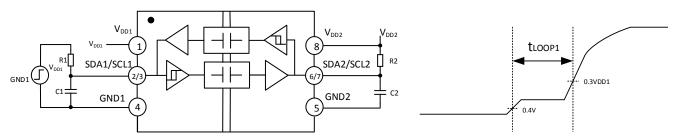

| Round-trip propagation delay on Side 1             | tLOOP1  |     | 104 | 156 | ns    | 0.4 V to 0.3 × $V_{DD1}$ ; R1 = 1430 $\Omega$ , R2 = 143 $\Omega$ , C1,C2 = 10 pF; @ 5 $V_{DC}$ supply                         |

|                                                    |         |     | 88  | 132 | ns    | R1 = 953 $\Omega$ ,R2 = 95.3 $\Omega$ ,C1, C2 = 10 pF; @ 3.3V <sub>DC</sub> supply                                             |

| Common-Mode Transient<br>Immunity <sup>2</sup>     | СМТІ    |     | 120 |     | kV/μs | $V_{IN} = V_{DDx}^{1}$ or 0V, $V_{CM} = 1000$ V.                                                                               |

| ESD(HBM - Human body<br>model)                     | ESD     |     | ±6  |     | kV    |                                                                                                                                |

Notes:

#### **INSULATION AND SAFETY RELATED SPECIFICATIONS**

**Table 7. Insulation Specifications**

|                                                                             |         | Value      |        | a !!!! /a .                                                                                                                |  |  |

|-----------------------------------------------------------------------------|---------|------------|--------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter                                                                   | Symbol  | M1251/1261 | Unit   | Test Conditions/Comments                                                                                                   |  |  |

| Rated Dielectric Insulation Voltage                                         |         | 3000       | V rms  | 1-minute duration                                                                                                          |  |  |

| Minimum External Air Gap<br>(Clearance)                                     | L (CLR) | 4          | mm min | Measured from input terminals to output terminals, shortest distance through air                                           |  |  |

| Minimum External Tracking (Creepage)                                        | L (CRP) | 4          | mm min | Measured from input terminals to output terminals, shortest distance path along body                                       |  |  |

| Minimum Clearance in the Plane of the Printed Circuit Board (PCB Clearance) | L (PCB) | 4.5        | mm min | Measured from input terminals to output terminals, shortest distance through air, line of sight, in the PCB mounting plane |  |  |

| Minimum Internal Gap (Internal Clearance)                                   |         | 21         | μm min | Insulation distance through insulation                                                                                     |  |  |

| Tracking Resistance (Comparative Tracking Index)                            | СТІ     | >400       | V      | DIN IEC 112/VDE 0303 Part 1                                                                                                |  |  |

| Material Group                                                              |         | II         |        | Material Group (DIN VDE 0110, 1/89, Table 1)                                                                               |  |  |

### **PACKAGE CHARACTERISTICS**

**Table 8. Package Characteristics**

| Parameter                                  | Symbol | Typical Value<br>ISO1541/1551 | Unit | Test Conditions/Comments |

|--------------------------------------------|--------|-------------------------------|------|--------------------------|

| Resistance (Input to Output) <sup>1</sup>  | Rı-o   | 10 <sup>11</sup>              | Ω    |                          |

| Capacitance (Input to Output) <sup>1</sup> | Cı-o   | 1.5                           | pF   | @1MHz                    |

| Input Capacitance <sup>2</sup>             | Cı     | 7                             | рF   | @1MHz                    |

$<sup>^{1}</sup>$  V<sub>DDx</sub> is the side voltage power supply V<sub>DD</sub>, where x = 1 or 2.

<sup>&</sup>lt;sup>2</sup>See Figure21 for Common-mode transient immunity (CMTI) measurement.

| Parameter                                    | Symbol        | Typical Value<br>M1251/1261 | Unit | Test Conditions/Comments                            |

|----------------------------------------------|---------------|-----------------------------|------|-----------------------------------------------------|

| IC Junction to Ambient<br>Thermal Resistance | $\theta_{JA}$ | 100                         | °C/W | Thermocouple located at center of package underside |

Notes:

## DIN V VDE V 0884-11 (VDE V 0884-11) INSULATION CHARACTERISTICS

These isolators are suitable for reinforced electrical isolation only within the safety limit data. Protective circuits ensure the maintenance of the safety data. The \* marking on packages denotes DIN V VDE V 0884-11 approval.

**Table 9. VDE Insulation Characteristics**

|                                               |                                                                                                   |                     | Characteristic |        |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------|----------------|--------|

| Description                                   | Test Conditions/Comments                                                                          | Symbol              | M1251/1261     | Unit   |

| Installation Classification per DIN VDE 0110  |                                                                                                   |                     |                |        |

| For Rated Mains Voltage $\leqslant$ 150 V rms |                                                                                                   |                     | I to IV        |        |

| For Rated Mains Voltage ≤ 300 V rms           |                                                                                                   |                     | I to III       |        |

| For Rated Mains Voltage ≤ 400 V rms           |                                                                                                   |                     | I to III       |        |

| Climatic Classification                       |                                                                                                   |                     | 40/105/21      |        |

| Pollution Degree per DIN VDE 0110, Table 1    |                                                                                                   |                     | 2              |        |

| Maximum repetitive peak isolation voltage     |                                                                                                   | VIORM               | 565            | V peak |

|                                               | $V_{IORM} \times 1.5 = V_{pd (m)}$ , 100% production                                              |                     |                |        |

| Input to Output Test Voltage, Method B1       | test, tini = t <sub>m</sub> = 1 sec, partial discharge < 5 pC                                     | V <sub>pd</sub> (m) | 848            | V peak |

| Input to Output Test Voltage, Method A        |                                                                                                   |                     |                |        |

| After Environmental Tests Subgroup 1          | $V_{IORM} \times 1.3 = V_{pd (m)}$ , $t_{ini} = 60$ sec, $t_m = 10$ sec, partial discharge < 5 pC | V <sub>pd (m)</sub> | 735            | V peak |

<sup>&</sup>lt;sup>1</sup>The device is considered a 2-terminal device; SOIC-8 Pin 1 - Pin 4 are shorted together as the one terminal, and SOIC-8 Pin 5 - Pin 8 are shorted together as the other terminal.

<sup>&</sup>lt;sup>2</sup>Testing from the input signal pin to ground.

| Description                             | Test Conditions/Comments                                                                                        | Symbol         | Characteristic ISO1541/1551 | Unit   |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------|-----------------------------|--------|

|                                         |                                                                                                                 |                |                             |        |

| Highest Allowable Overvoltage           |                                                                                                                 | Vіотм          | 4200                        | V peak |

| Surge Isolation Voltage Basic           | Basic insulation, 1.2 $\mu$ s rise time, 50 $\mu$ s, 50% fall time , VTEST = 1.3 $\times$ VIOSM (qualification) | Viosm          | 3615                        | V peak |

| Surge Isolation Voltage Reinforced      | Reinforced insulation, 1.2 $\mu$ s rise time, 50 $\mu$ s, 50% fall time                                         | Viosm          |                             | V peak |

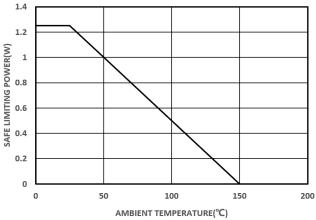

| Safety Limiting Values                  | Maximum value allowed in the event of a failure (see Figure 4)                                                  |                |                             |        |

| Maximum Junction Temperature            |                                                                                                                 | T <sub>S</sub> | 150                         | °C     |

| Maximum Power Dissipation at 25°C       |                                                                                                                 | $P_S$          | 1.25                        | w      |

| Insulation Resistance at T <sub>S</sub> | V <sub>IO</sub> = 500 V                                                                                         | $R_S$          | >10 <sup>9</sup>            | Ω      |

## **Typical Thermal Characteristic**

Figure 4. Thermal Derating Curve, Dependence of Safety Limiting Values with Ambient Temperature per VDE

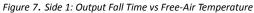

Figure 6. Side 1: Output Fall Time vs Free-Air Temperature

Figure 8. Side 2: Output Fall Time vs Free-Air Temperature

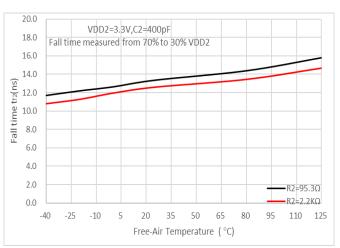

Figure 9. Side 2: Output Fall Time vs Free-Air Temperature

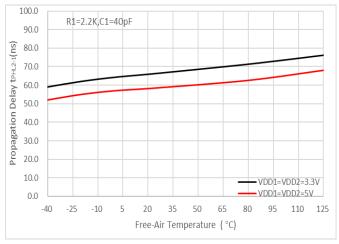

Figure 10.  $t_{PLH1-2}$  Propagation Delay vs Free-Air Temperature

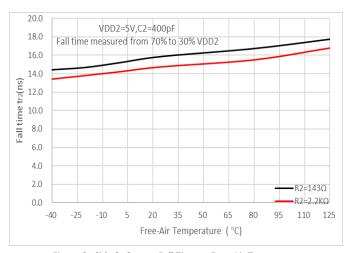

Figure 11. tphl1-2 Propagation Delay vs Free-Air Temperature

Figure 12. tplh1-2 Propagation Delay vs Free-Air Temperature

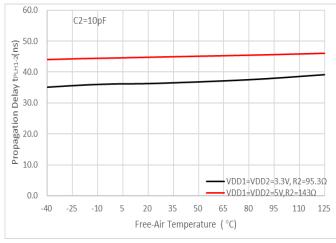

500.0

R1=2.2K,C1=40pF

Figure 13. tphl2-1 Propagation Delay vs Free-Air Temperature

Figure 14. tplh2-1 Propagation Delay vs Free-Air Temperature

Figure 15. tphl2-1 Propagation Delay vs Free-Air Temperature

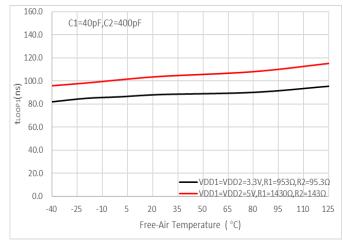

Figure 16. tloop1 vs Free-Air Temperature

#### PARAMETER MEASUREMENT INFORMATION

Figure 17. Test Diagram

Figure 18. tLoop1 Setup and Timing Diagram

Figure 19. Common-Mode Transient Immunity Test Circuit

## **APPLICATIONS INFORMATION**

#### Overview

The inter-integrated circuit (I<sup>2</sup>C) bus is a single-ended, two wire bus for efficient inter-IC communication and is used in a wide range of applications. The I<sup>2</sup>C bus is used for communication between multiple masters or a single master and slaves. The master device controls the serial clock line (SCL) and data is bidirectional transferred on the serial data line (SDA) between master and slaves. The I<sup>2</sup>C bus can theoretically add up to 112 communication nodes, however, the number of nodes will increase the load capacitance on the bus, thereby limiting the communication distances and communication speeds. In applications, tradeoffs are often made between communication speeds, bus length, and number of nodes based on actual conditions.

The 1<sup>2</sup>C bus supports data transmission in four speeds: standard mode (up to 100Kbps), fast mode (up to 400Kbps), fast mode plus (up to 1Mbps), and high-speed mode (up to 3.4Mbps). The M1251/1261 devices support all the above four communication modes.

#### **FUNCTIONAL DESCRIPTION**

The M1251/1261 devices are low-power bidirectional isolators compatible with the I<sup>2</sup>C interface and are based on

**iDivider®** technology from 2PaiSemi. These devices have logic input and output buffers that are separated by using a silicon dioxide (SiO<sub>2</sub>) barrier. These devices block high voltages and prevent noise currents from entering the control side ground, avoiding circuit interference and damaging sensitive components. Each channel output of the ISO1251/1261 devices is made open-drain to comply with the open-drain technology of I<sup>2</sup>C. Serial data line (SDA)and serial clock line (SCL) need to add pull-up resistors to ensure normal operation of the system. It is recommended that side 1 of the I<sup>2</sup>C isolator be connected to the processor and sides 2 to the bus when there are multiple nodes on the I<sup>2</sup>C bus as side 2 support up to 400 pF capacitance load.

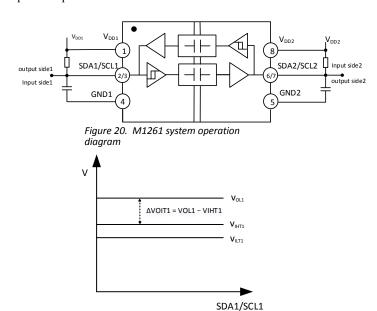

The M1251 devices feature two bidirectional channels that have open-drain outputs, As shown in Figure 20. As a logic low on one side causes the corresponding pin on the other side to be pulled low, to avoid data-latching within the device, The output logic low (VOL1)voltages of SDA1 and SCL1 are at least 60mV higher than the input threshold high (VIHT1) of SDA1 and SCL1, As shown in Figure 21.

Because the Side 2 logic levels/thresholds are standard  $I^2C$  values, multiple  $M_{1251/1261}$  devices connected to a bus by their Side 2 pins can communicate with each other and with other  $I^2C$  compatible devices. However, because the Side 1 pin has a modified output level/ input threshold, this side of the  $M_{1251/1261}$  can communicate only with devices that conform to the  $I^2C$  standard.

The output low voltages of  $M_{1251/1261}$  devices are guaranteed for sink currents of up to 35mA for side 2, and 3.5mA for side 1.

To enhance system reliability, it is recommended to connect the node with larger load capacitance and longer wires on side 2 for point-to-point communication.

Figure 21. M1251/1261 side 1 voltage Diagram

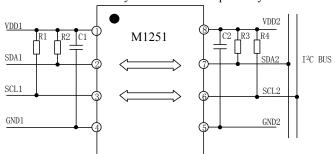

#### TYPICAL APPLICATION DIAGRAM

Figure 22 shows a typical application circuit including the pull-up resistors required for both Side 1 and Side 2. Bypass capacitors with values from  $0.1\mu F$  to  $10\mu F$  are required between  $V_{DD1}$  and GND1 and between  $V_{DD2}$  and GND2. To enhance the robustness of a design, the user may connect a resistor (50-200  $\Omega$ ) in series between R2 and C1 and between R3 and C2 if the system is excessively noisy.

The M1251/1261 are designed for operation at speeds up to 2 MHZ. Due to the limited current available on side 1 and side2, operation at 2MHZ limits the capacitance that can be driven at the minimum pull-up value to 40pF and 400pF.

Most applications operate at 100 kbps in standard mode or 400 kbps in fast mode. At these lower operating speeds, the limitation on the load capacitance can be significantly relaxed. If larger values for the pull up resistor are used, the maximum supported capacitance must be scaled down proportionately so that the rise time does not increase beyond the values required by the standard.

Figure 22. Typical Isolated I<sup>2</sup>C Interface Using the M1251

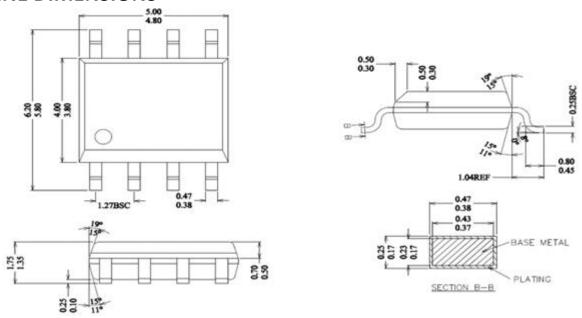

# **OUTLINE DIMENSIONS**

Notes:

ALL DIMENSIONS REFER TO JEDEC STANDARD MS—012 AA

DO NOT INCLUDE MOLD FLASH OR PROTRUSION.

Figure 23. 8-Lead Narrow Body SOIC [NB SOIC-8] Outline Package – dimension unit(mm)

## **REEL INFORMATION**

8-Lead Narrow Body SOIC [NB SOIC-8]

Note: The Pin 1of the chip is in the quadrant Q1

Figure 24. 8-Lead Narrow Body SOIC [NB SOIC-8] Reel Information—dimension unit(mm)