### **FEATURES**

### PRODUCT APPEARANCE

- LIN 2.x/ISO 17987-4:2016 (12V)/SAE J2602 compliant

- > Thermally protected

- > Transmit data (TXD) dominant time-out function

- > Bus terminal current limit protected

- Under voltage on battery

- Very low current consumption in Sleep mode

- Support local and remote wake-up

- Enable an external high voltage regulator by INH

- ➤ Baud rates up to 20 kBd

- Very low ElectroMagnetic Emission (EME)

- ➤ High ElectroMagnetic Immunity (EMI)

- ➤ Available in SO8 and DFN3\*3-8 packages

Fig 1. Provide green and environmentally friendly lead-free package

### **DESCRIPTION**

The SIT1021 is a physical layer transceiver of Local Interconnect Network (LIN). It is compliant with LIN 2.0/LIN 2.1/LIN 2.2/LIN 2.2A/ISO 17987-4:2016 (12V) and SAE J2602 standards. It is typically used for low speed in-vehicle networks using baud rates from 1 kBd to 20 kBd. The LIN protocol data stream at the transmit data input (TXD) is converted by the SIT1021 into a bus signal with optimized wave shaping to minimize ElectroMagnetic Emission (EME). The SIT1021 converts the data stream on LIN bus to logic level signals that are sent to the microprocessor via the pin RXD. The LIN bus is pulled high by the internal slave resistor and a series diode. Master applications require an external pull-up resistor in series with a diode to connect pin VBAT and pin LIN.

The SIT1021 has an extremely low current consumption in sleep mode. The power consumption is reduced to a minimum if in failure modes. It also provides a high voltage output pin INH to enable an external high voltage regulator which used to support the microprocessor.

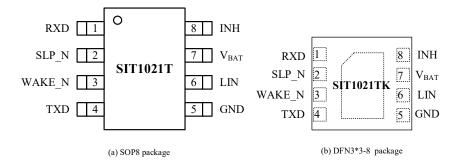

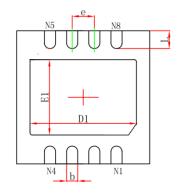

### PIN CONFIGURATION

Fig 2. SIT1021 pin configuration diagrams

## PIN DESCRIPTION

Table 1. Pin description

| Pin | Symbol             | Description                                                                                                            |  |  |  |

|-----|--------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | RXD                | receive data output (open-drain); active LOW after a wake-up event.                                                    |  |  |  |

| 2   | SLP_N              | leep control input (active LOW); controls inhibit output; resets wake-up ource flag on TXD and wake-up request on RXD. |  |  |  |

| 3   | WAKE_N             | ocal wake-up input (active LOW); negative edge triggered.                                                              |  |  |  |

| 4   | TXD                | transmit data input; active LOW output after a local wake-up event.                                                    |  |  |  |

| 5   | GND                | Ground.                                                                                                                |  |  |  |

| 6   | LIN                | LIN bus line input/output.                                                                                             |  |  |  |

| 7   | $V_{\mathrm{BAT}}$ | battery supply voltage.                                                                                                |  |  |  |

| 8   | INH                | battery related inhibit output for controlling an external voltage regulator; active HIGH after a wake-up event.       |  |  |  |

NOTE: The exposed center pad of the DFN3\*3-8 package is internal connected to the GND PIN of the Chip. For enhanced thermal performance, the exposed center pad of the DFN3\*3-8 package could be soldered to board ground.

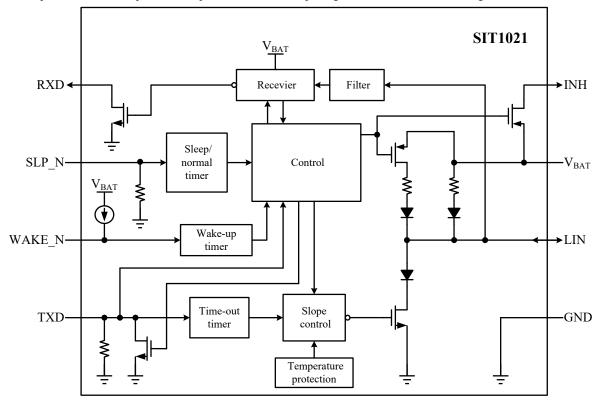

Fig 3. Block diagram

### FEATURE DESCRIPTION

#### 1 Overview

The SIT1021 is an interface device used between the LIN protocol controller and the physical bus. It can be used for in-vehicle and industrial control with a data rate up to 20kBd. The SIT1021 receives the data stream sent by protocol controller at the pin TXD, and converts it into a bus signal with appropriate slew rate and waveform shaping. The input data on LIN bus is output to external microcontroller by pin RXD. This device is compliant with LIN 2.0/LIN 2.1/LIN 2.2/LIN 2.2A/ISO 17987-4:2016 (12V) and SAE J2602 standards.

#### 2 Short-circuit protection

Pin TXD provides an internal pull-down to GND to apply a predefined level on TXD when it is not enabled. The pin SLP\_N also provides an internal pull-down to force the transceiver to enter sleep mode when SLP N is not enabled.

Pin RXD will be left floating and limit the output current of transmitter to prevent a short-circuit between LIN and VBAT or GND if the supply on pin VBAT is turned off. There is no reverse current at the bus terminal, and the connection between LIN supply can be shut off without affecting the bus.

#### 3 Thermal Shutdown

In normal mode, the over-temperature protection circuit will disable the output driver when the junction temperature of SIT1021 exceeds the shutdown junction temperature  $T_{j(sd)}$ . The driver is enabled again when the junction temperature has dropped below  $T_{j(sd)}$  and a recessive level is present at pin TXD.

#### 4 TXD dominant time-out function

A TXD dominant time-out timer circuit prevents the bus lines from being driven to a permanent dominant state (blocking all network communication) if pin TXD is forced permanently LOW by a hardware and/or software application failure. The timer is triggered by a negative edge on pin TXD. If the duration of the LOW level on pin TXD exceeds the internal timer value ( $t_{dom}$ ), the transmitter is disabled, driving the bus lines into a recessive state. The timer is reset by a positive edge on pin TXD.

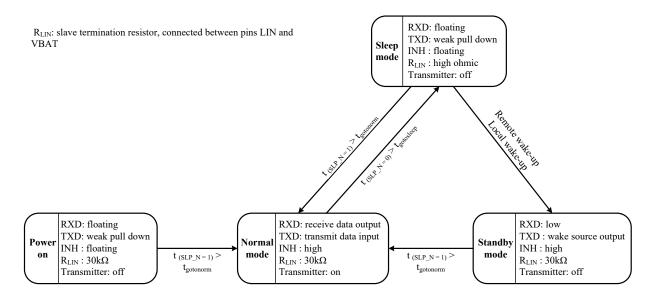

#### 5 Operating modes

As shown in <u>Fig 4</u>, the SIT1021 supports four functional modes for normal operation (Normal mode), power-up (Power-on mode), standby operation (Standby mode) and very-low-power operation (Sleep mode). The operating states in each mode are shown in <u>Table 2</u>.

**Sleep mode:** This mode is the most power saving mode of the SIT1021. It can be woken up remotely via pin LIN, or woken up locally via pin WAKE\_N, or activated directly via pin SLP\_N. The pin WAKE\_N, pin SLP\_N and pin LIN are filtered to prevent accidental wake up events. The wake-up events for SIT1021 in sleep mode is: the remote wake up time via pin LIN must be longer than t<sub>wake(dom)LIN</sub>; the local wake up time via pin WAKE\_N must be longer than t<sub>wake(dom)WAKE\_N</sub>; the time wake up directly via pin SLP\_N must be

longer than t<sub>gotonorm</sub>.

Sleep mode is only entered when the pin SLP\_N is low and from normal mode. To enter Sleep mode successfully (INH becomes floating), the sleep command (SLP\_N = 0) must be maintained for at least  $t_{gotosleep}$ . The pin INH is only floating in sleep mode and going into high in others modes.

**Standby mode:** It is entered whenever a local or remote wake-up occurs while the device is in Sleep mode. Standby mode is signaled through a low level on pin RXD. The pin INH will be set high and activate the external voltage regulator and the microcontroller after the device enters standby mode from sleep mode. Setting pin SLP N high during Standby mode results in the following events:

- (1) An immediate reset of the wake-up source flag; thus, releasing the possible strong pull-down at pin TXD before the actual mode change (after t<sub>gotonorm</sub>) is performed.

- (2) A change into Normal mode if the high level on pin SLP\_N has been maintained for a certain time period (tgotonorm).

- (3) An immediate reset of the wake-up request signal on pin RXD.

**Normal mode:** Only in Normal mode the receiver and transmitter are active and the SIT1021 is able to transmit and receive data via the LIN bus. The high level of bus represents recessive and low level represents dominant. The receiver detects the data stream on the LIN bus and outputs it to the microcontroller via pin RXD. Normal mode is entered as a high level on pin SLP\_N and maintained for a time of at least t<sub>gotonorm</sub> while the SIT1021 is in Sleep, Power-up or Standby mode. The Sleep mode is entered by setting pin SLP\_N low for longer than t<sub>gotosleep</sub>.

**Power-on mode:** When SIT1021 is in Power-on mode: pin RXD is left floating, pin TXD is weakly pulled down, transmitter and receiver are not activated. If the pin SLP\_N is high at power up the device will power up in normal mode and if low will power up in standby mode.

#### 6 Wake-up source recognition

In Sleep mode, SIT1021 can wake up remotely via the LIN bus or wake up locally via the pin WAKE\_N. The wake-up source flag can be read by detecting the state of pin TXD in the Standby mode. If an external pull-up resistor on pin TXD to the power supply voltage of the microcontroller has been added, a high level indicates a remote wake-up request (weak pull-down at pin TXD) and a LOW level indicates a local wake-up request (strong pull-down at pin TXD; much stronger than the external pull-up resistor). The wake-up request flag (signaled on pin RXD) as well as the wake-up source flag (signaled on pin TXD) are reset immediately after the microcontroller sets pin SLP\_N high.

#### 7 Wake Up Events

In sleep mode, the device can be woken up by the following three ways:

- (1) Remote wake-up via pin LIN;

- (2) Local wake-up via pin WAKE N;

- (3) Wake up directly via pin SLP\_N.

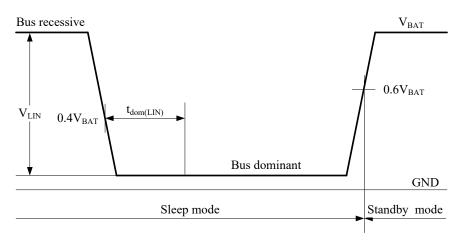

#### 8 Remote and local wake-up

Remote wake-up on the pin LIN: When A falling edge at pin LIN followed by a low level maintained longer than  $t_{wake(dom)LIN}$  and a rising edge at pin LIN respectively, the process is regarded as a valid remote wake-up event (see Fig 5).

Local wake-up on the pin WAKE\_N: When A falling edge at pin LIN followed by a low level maintained longer than t<sub>wake(dom)WAKE\_N</sub>, the process is regarded as a valid remote wake-up event. The pin WAKE\_N provides an internal pull-up path to VBAT. To prevent EMI issues, it is recommended to connect the unused pin WAKE N to VBAT.

When a local or remote wake-up occurs, pin INH is activated (turns to high) and the internal slave termination resistor is turned on. The wake-up request is indicated by a low active wake-up request signal on pin RXD to interrupt the microcontroller.

Fig 4. State diagram

Table 2. Operating modes

| Mode     | SLP_N | TXD                                                                 | RXD                           | INH      | Transmitter | Remarks                                                                                                         |

|----------|-------|---------------------------------------------------------------------|-------------------------------|----------|-------------|-----------------------------------------------------------------------------------------------------------------|

| Sleep    | low   | weak pull-down                                                      | floating                      | floating | off         | no wake-up request detected                                                                                     |

| Standby  | low   | weak pull-down if remote wake-up; strong pull-down if local wake-up | low                           | high     | off         | wake-up request detected; in this mode the microcontroller can read the wake-up source: remote or local wake-up |

| Normal   | high  | recessive: high dominant: low                                       | recessive: high dominant: low | high     | on          |                                                                                                                 |

| Power-on | low   | weak pull-down                                                      | floating                      | high     | off         |                                                                                                                 |

Fig 5. Remote wake-up behavior

## LIMITING VALUES

| Parameter                    | Symbol              | Conditions                       | Range                     | Unit |

|------------------------------|---------------------|----------------------------------|---------------------------|------|

| battery supply voltage       | $V_{\mathrm{BAT}}$  | with respect to GND              | -0.3 ~ +42                | V    |

| voltage on nin TVD           | V                   | I <sub>SLP_N</sub> no limitation | <b>-</b> 0.3 ∼ +6         | V    |

| voltage on pin TXD           | $V_{TXD}$           | $I_{SLP\_N} < 500 \mu A$         | <b>-</b> 0.3 ∼ +7         | v    |

| velta as an nin DVD          | 17                  | $I_{SLP\_N}$ no limitation       | <b>-</b> 0.3 ∼ +6         | V    |

| voltage on pin RXD           | $V_{RXD}$           | $I_{SLP\_N}$ < 500 $\mu$ A       | <b>-</b> 0.3 ∼ +7         | v    |

| lt                           | 37                  | $I_{SLP\_N}$ no limitation       | <b>-</b> 0.3 ∼ +6         | V    |

| voltage on pin SLP_N         | $ m V_{SLP\_N}$     | $I_{SLP\_N}$ < 500 $\mu$ A       | <b>-</b> 0.3 ∼ +7         | v    |

| voltage on pin LIN           | $V_{LIN}$           | with respect to GND              | -42 ~ +42                 | V    |

| voltage on pin WAKE_N        | V <sub>WAKE_N</sub> |                                  | <b>-</b> 0.3 ∼ +42        | V    |

| voltage on pin INH           | $V_{\rm INH}$       |                                  | $-0.3 \sim V_{BAT} + 0.3$ | V    |

| virtual junction temperature | Tj                  |                                  | -40 ~ 150                 | °C   |

| storage temperature          | $T_{stg}$           |                                  | <b>-</b> 55 ∼ 150         | °C   |

The maximum limit parameters mean that exceeding these values may cause irreversible damage to the device. Under these conditions, it is not conducive to the normal operation of the device. The continuous operation of the device at the maximum allowable rating may affect the reliability of the device. The reference point for all voltages is ground.

# STATIC CHARACTERISTICS

| Parameter                                                                                                  | Symbol                                | Conditions                                                                                                                                                                             | Min  | Тур | Max  | Unit |

|------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| Supply                                                                                                     |                                       |                                                                                                                                                                                        |      |     |      |      |

|                                                                                                            |                                       | Sleep mode; $(V_{LIN} = V_{BAT}; \\ V_{WAKE\_N} = V_{BAT}; \\ V_{TXD} = 0V; V_{SLP\_N} = 0V)$                                                                                          | 1    | 3   | 15   | μΑ   |

| battery supply current                                                                                     | Іват                                  | $\label{eq:Standby mode;} Standby mode; \\ bus recessive \\ (V_{INH}=V_{BAT}; \\ V_{LIN}=V_{BAT}; \\ V_{WAKE\_N}=V_{BAT}; \\ V_{TXD}=0V; V_{SLP\_N}=0V)$                               | 150  | 350 | 800  | μΑ   |

|                                                                                                            |                                       | Standby mode;<br>bus dominant<br>(V <sub>BAT</sub> =12V;<br>V <sub>INH</sub> =12V; V <sub>LIN</sub> =0V;<br>V <sub>WAKE_N</sub> =12V;<br>V <sub>TXD</sub> =0V; V <sub>SLP_N</sub> =0V) | 500  | 750 | 1000 | μА   |

|                                                                                                            |                                       | Normal mode;<br>bus recessive<br>$(V_{INH}=V_{BAT};$<br>$V_{LIN}=V_{BAT};$<br>$V_{WAKE\_N}=V_{BAT};$<br>$V_{TXD}=5V; V_{SLP\_N}=5V)$                                                   | 200  | 380 | 600  | μΑ   |

|                                                                                                            |                                       | Normal mode;<br>bus dominant<br>$(V_{BAT}=12V;$<br>$V_{INH}=12V;$<br>$V_{WAKE\_N}=12V;$<br>$V_{TXD}=0V;$ $V_{SLP\_N}=5V)$                                                              | 0.5  | 1.4 | 3    | mA   |

| Power-on reset                                                                                             |                                       |                                                                                                                                                                                        |      |     |      |      |

| $\begin{array}{c} \text{low-level V}_{\text{BAT}} \\ \text{reset threshold} \\ \text{voltage} \end{array}$ | $V_{\text{th}}(V_{\text{BATL}})L$     |                                                                                                                                                                                        | 3.9  | 4.4 | 4.7  | V    |

| high-level V <sub>BAT</sub> reset threshold voltage                                                        | $V_{th}(V_{BATL})H$                   |                                                                                                                                                                                        | 4.2  | 4.7 | 5.1  | V    |

| V <sub>BAT</sub> reset<br>hysteresis voltage                                                               | V <sub>hys</sub> (V <sub>BATL</sub> ) |                                                                                                                                                                                        | 0.05 | 0.3 | 1    | V    |

| Parameter                               | Symbol                 | Conditions                                                                                     | Min                 | Тур | Max                   | Unit |

|-----------------------------------------|------------------------|------------------------------------------------------------------------------------------------|---------------------|-----|-----------------------|------|

| Pin TXD                                 |                        | •                                                                                              |                     |     |                       |      |

| high-level input voltage                | $V_{ m IH}$            |                                                                                                | 2                   |     | 7                     | V    |

| low-level input voltage                 | $ m V_{IL}$            |                                                                                                | -0.3                |     | +0.8                  | V    |

| hysteresis voltage                      | $V_{\mathrm{hys}}$     |                                                                                                | 50                  | 200 | 400                   | mV   |

| pull-down<br>resistance on pin<br>TXD   | R <sub>PD(TXD)</sub>   | V <sub>TXD</sub> =5V                                                                           | 140                 | 500 | 1200                  | kΩ   |

| low-level input current                 | $I_{\mathrm{IL}}$      | V <sub>TXD</sub> =0V                                                                           | -5                  |     | +5                    | μΑ   |

| low-level output<br>current             | Iol                    | local wake-up request; Standby mode; $V_{WAKE\_N}{=}0V;$ $V_{LIN}{=}V_{BAT};$ $V_{TXD}{=}0.4V$ | 1.5                 |     |                       | mA   |

| Pin SLP_N                               | •                      |                                                                                                |                     | •   | •                     |      |

| high-level input voltage                | V <sub>IH</sub>        |                                                                                                | 2                   |     | 7                     | V    |

| low-level input voltage                 | V <sub>IL</sub>        |                                                                                                | -0.3                |     | 0.8                   | V    |

| hysteresis voltage                      | $V_{hys}$              |                                                                                                | 50                  | 200 | 400                   | mV   |

| pull-down<br>resistance on pin<br>SLP_N | R <sub>PD(SLP_N)</sub> | V <sub>SLP_N</sub> =5V                                                                         | 140                 | 500 | 1200                  | kΩ   |

| low-level input current                 | $I_{IL}$               | V <sub>SLP_N</sub> =0V                                                                         | -5                  |     | 5                     | μΑ   |

| Pin RXD                                 |                        |                                                                                                |                     |     |                       |      |

| low-level output                        | Iol                    | Normal mode; $V_{RXD}{=}0.4V;$ $V_{LIN}{=}0V$                                                  | 1.5                 |     |                       | mA   |

| high-level leakage current              | $I_{LH}$               | Normal mode; $V_{RXD}=5V;$ $V_{LIN}=V_{BAT}$                                                   | -5                  |     | 5                     | μΑ   |

| Pin WAKE_N                              |                        |                                                                                                |                     |     |                       | _    |

| high-level input voltage                | $V_{ m IH}$            |                                                                                                | V <sub>BAT</sub> -1 |     | V <sub>BAT</sub> +0.3 | V    |

| low-level input voltage                 | V <sub>IL</sub>        |                                                                                                | -0.3                |     | V <sub>BAT</sub> -3.3 | V    |

| Parameter                                                          | Symbol                   | Conditions                                                                                                        | Min                   | Тур                    | Max                   | Unit |

|--------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|-----------------------|------|

| low-level pull-up current                                          | $I_{pu(L)}$              | V <sub>WAKE_N</sub> =0V;                                                                                          | -30                   | -12                    | -1                    | μΑ   |

| high-level leakage current                                         | $I_{LH}$                 | $V_{WAKE\_N}$ =27V;<br>$V_{BAT}$ =27V                                                                             | -5                    |                        | 5                     | μΑ   |

| Pin INH                                                            |                          |                                                                                                                   |                       |                        |                       |      |

| switch-on resistance between pins $V_{BAT}$ and INH                | R <sub>SW</sub>          | Standby; Normal and Power-on mode; I <sub>INH</sub> =-15mA; V <sub>BAT</sub> =12V                                 |                       | 20                     | 50                    | Ω    |

| high-level leakage current                                         | $I_{LH}$                 | Sleep mode;<br>V <sub>INH</sub> =27V; V <sub>BAT</sub> =27V                                                       | -5                    |                        | 5                     | μΑ   |

| Pin LIN                                                            |                          |                                                                                                                   |                       |                        |                       |      |

| current limitation<br>for driver dominant<br>state                 | I <sub>BUS_LIM</sub>     | V <sub>TXD</sub> =0V;<br>V <sub>LIN</sub> =V <sub>BAT</sub> =18V                                                  | 40                    |                        | 100                   | mA   |

| pull-up resistance                                                 | $R_{pu}$                 | Sleep mode;<br>V <sub>SLP_N</sub> =0V                                                                             | 50                    | 160                    | 250                   | kΩ   |

| receiver recessive input leakage current                           | I <sub>BUS_PAS_rec</sub> | $V_{TXD}$ =5V;<br>$V_{LIN}$ =27V; $V_{BAT}$ =5.5V                                                                 |                       |                        | 10                    | μΑ   |

| receiver dominant input leakage current including pull-up resistor | IBUS_PAS_dom             | Normal mode; $V_{TXD}{=}5V;$ $V_{LIN}{=}0V; V_{BAT}{=}12V$                                                        | -1000                 |                        |                       | μΑ   |

| loss-of-ground bus current                                         | I <sub>BUS_NO_GND</sub>  | V <sub>BAT</sub> =27V; V <sub>LIN</sub> =0V                                                                       | -1000                 |                        | 10                    | μΑ   |

| loss-of-battery bus current                                        | I <sub>BUS_NO_BAT</sub>  | $V_{BAT}=0V; V_{LIN}=27V$                                                                                         |                       |                        | 10                    | μΑ   |

| receiver dominant input voltage                                    | $V_{\text{th(dom)RX}}$   |                                                                                                                   |                       |                        | $0.4 { m V}_{ m BAT}$ | V    |

| receiver recessive input voltage                                   | $V_{\text{th(rec)RX}}$   |                                                                                                                   | $0.6 { m V}_{ m BAT}$ |                        |                       | V    |

| receiver center voltage                                            | V <sub>th(RX)cntr</sub>  | $ \begin{array}{c} V_{\text{th(RX) cntr}} \!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | 0.475V <sub>BAT</sub> | $0.5~\mathrm{V_{BAT}}$ | $0.525 V_{BA}$        | V    |

| receiver hysteresis voltage                                        | V <sub>th(hys)RX</sub>   | $\begin{array}{c} V_{th(hys)RX} = \\ V_{th(rec)RX} - V_{th(dom)RX} \end{array}$                                   |                       |                        | 0.175V <sub>BA</sub>  | V    |

| slave resistance                                                   | R <sub>slave</sub>       | connected between pins LIN and $V_{BAT}$ ; $V_{LIN}=0V; V_{BAT}=12V;$ $V_{TXD}=V_{SLP\_N}=5V$                     | 20                    | 30                     | 60                    | kΩ   |

| Parameter                     | Symbol       | Conditions                                                  | Min | Тур | Max | Unit |

|-------------------------------|--------------|-------------------------------------------------------------|-----|-----|-----|------|

| capacitance on pin LIN        | $C_{LIN}$    |                                                             |     |     | 30  | pF   |

| dominant output               | $V_{o(dom)}$ | Normal mode;<br>V <sub>TXD</sub> =0V; V <sub>BAT</sub> =7V  |     |     | 1.4 | V    |

| voltage                       |              | Normal mode;<br>V <sub>TXD</sub> =0V; V <sub>BAT</sub> =18V |     |     | 2.0 | V    |

| Thermal shutdown              |              |                                                             |     |     |     |      |

| shutdown junction temperature | $T_{j(sd)}$  |                                                             | 150 | 175 | 200 | °C   |

(Unless specified otherwise;  $5.5V \le V_{BAT} \le 27V$ ,  $-40^{\circ}C \le T_{j} \le 150^{\circ}C$ ; typical in  $V_{BAT} = 12V$ ,  $T_{amb} = 25^{\circ}C$ .)

# DYNAMIC CHARACTERISTICS

| Parameter    | Symbol    | Conditions                                                                                                                                                                                                                                   | Min   | Тур | Max   | Unit |

|--------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

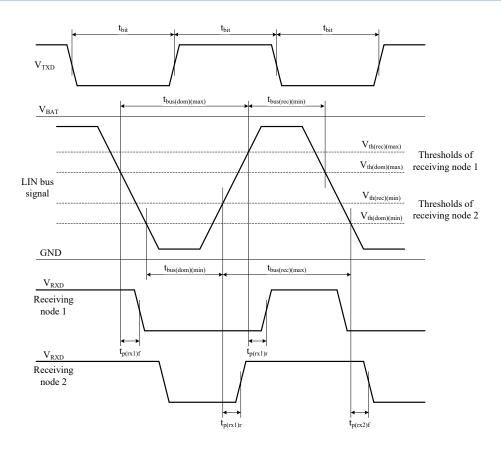

| Duty cycles  |           |                                                                                                                                                                                                                                              |       |     |       |      |

| duty cycle 1 | S1 [1][2] | $\begin{array}{c} V_{th(rec)(max)}\!\!=\!\!0.744\!\times\!V_{BAT};\\ V_{th(dom)(max)}\!\!=\!\!0.581\!\times\!V_{BAT};\\ t_{bit}\!\!=\!\!50\mu s;\\ V_{BAT}\!\!=\!\!7V\!\!\sim\!\!18V \qquad \underline{Fig~6} \end{array}$                   | 0.396 |     |       |      |

|              | δ1 [1][2] | $\begin{tabular}{ll} $V_{th(rec)(max)}$=$0.76$\times$V_{BAT};\\ $V_{th(dom)(max)}$=$0.593$\times$V_{BAT};\\ $t_{bit}$=$50$\mus;\\ $V_{BAT}$=$5.5V$\sim$7V                                  $                                                 | 0.396 |     |       |      |

| duty cycle 2 | SO [3][3] | $\begin{array}{c} V_{th(rec)(min)}\!\!=\!\!0.422\!\times\!V_{BAT};\\ V_{th(dom)(min)}\!\!=\!\!0.284\!\times\!V_{BAT};\\ t_{bit}\!\!=\!\!50\mu s;\\ V_{BAT}\!\!=\!\!7.6V\!\!\sim\!\!18V  \underline{Fig~6} \end{array}$                       |       |     | 0.581 |      |

|              | 82 [2][3] | $ \begin{array}{c} V_{th(rec)(min)} \!\!=\!\! 0.41 \!\times\! V_{BAT}; \\ V_{th(dom)(min)} \!\!=\!\! 0.275 \!\times\! V_{BAT}; \\ t_{bit} \!\!=\!\! 50 \mu s; \\ V_{BAT} \!\!=\!\! 6.1 V \!\!\sim\!\! 7.6 V  \underline{Fig~6} \end{array} $ |       |     | 0.581 |      |

| duty cycle 3 | 83 [1][2] | $\begin{array}{c} V_{th(rec)(max)}\!\!=\!\!0.778\!\times\!V_{BAT};\\ V_{th(dom)(max)}\!\!=\!\!0.616\!\times\!V_{BAT};\\ t_{bit}\!\!=\!\!96\mu s;\\ V_{BAT}\!\!=\!\!7V\!\!\sim\!\!18V \qquad \underline{Fig~6} \end{array}$                   | 0.417 |     |       |      |

|              |           | $\begin{array}{c} V_{th(rec)(max)}\!\!=\!\!0.797\!\times\!V_{BAT};\\ V_{th(dom)(max)}\!\!=\!\!0.630\!\times\!V_{BAT};\\ t_{bit}\!\!=\!\!96\mu s;\\ V_{BAT}\!\!=\!\!5.5V\!\!\sim\!\!7V \qquad \underline{Fig~6} \end{array}$                  | 0.417 |     |       |      |

| Parameter                                 | Symbol                     | ool Conditions                                                                                                                                                                                                                                    |    | Тур | Max   | Unit |  |

|-------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|-------|------|--|

|                                           | 84 [2][3]                  | $\begin{array}{c} V_{th(rec)(min)}\!\!=\!\!0.389\!\times\!V_{BAT};\\ V_{th(dom)(min)}\!\!=\!\!0.251\!\times\!V_{BAT};\\ t_{bit}\!\!=\!\!96\mu s;\\ V_{BAT}\!\!=\!\!7.6V\!\!\sim\!\!18V  \underline{Fig~6} \end{array}$                            |    |     | 0.590 |      |  |

| duty cycle 4                              | 04 (2)(3)                  | $ \begin{array}{c} V_{th(rec)(min)} \!\!=\!\! 0.378 \! \times \! V_{BAT}; \\ V_{th(dom)(min)} \!\!=\!\! 0.242 \! \times \! V_{BAT}; \\ t_{bit} \!\!=\!\! 96 \mu s; \\ V_{BAT} \!\!=\!\! 6.1 V \!\!\sim\!\! 7.6 V  \underline{Fig~6} \end{array} $ |    |     | 0.590 |      |  |

| Timing characterist                       | Timing characteristics     |                                                                                                                                                                                                                                                   |    |     |       |      |  |

| receiver propagation delay                | t <sub>PD(RX)</sub> [4]    |                                                                                                                                                                                                                                                   |    |     | 6     | μs   |  |

| receiver<br>propagation delay<br>symmetry | t <sub>PD(RX)sym</sub> [4] |                                                                                                                                                                                                                                                   | -2 |     | 2     | μs   |  |

| LIN dominant wake-up time                 | twake(dom)LIN              | Sleep mode                                                                                                                                                                                                                                        | 30 | 65  | 150   | μs   |  |

| dominant wake-up<br>time on pin<br>WAKE_N | twake(dom)WAKE_N           | Sleep mode                                                                                                                                                                                                                                        | 7  | 22  | 50    | μs   |  |

| go to normal time                         | $t_{\mathrm{gotonorm}}$    |                                                                                                                                                                                                                                                   | 2  | 5   | 10    | μs   |  |

| go to sleep time                          | $t_{ m gotosleep}$         |                                                                                                                                                                                                                                                   | 2  | 5   | 10    | μs   |  |

| TXD dominant time-out time                | $t_{to(dom)TXD}$           | V <sub>TXD</sub> =0V                                                                                                                                                                                                                              | 27 | 52  | 90    | ms   |  |

(Unless specified otherwise;  $5.5 \text{V} \le \text{V}_{BAT} \le 27 \text{V}$ ,  $-40^{\circ}\text{C} \le \text{T}_{j} \le 150^{\circ}\text{C}$ ; typical in  $\text{V}_{BAT} = 12 \text{V}$ ,  $\text{T}_{amb} = 25^{\circ}\text{C}$ .)

[1]

$$\delta 1, \delta 3 = \frac{t_{bus(rec)(min)}}{2 \times t_{bit}}$$

.

[2] Bus load conditions are: (1)  $C_L=1$ nF,  $R_L=1$ k $\Omega$ ; (2)  $C_L=6.8$ nF,  $R_L=660$  $\Omega$ ; (3)  $C_L=1$ 0nF,  $R_L=500$  $\Omega$ .

[3]

$$\delta 2, \delta 4 = \frac{t_{bus(rec)(max)}}{2 \times t_{bit}}$$

.

[4] Load condition pin RXD: C\_TXD=20pF, R\_RXD=2.4k  $\!\Omega.$

Fig 6. Timing diagram LIN transceiver

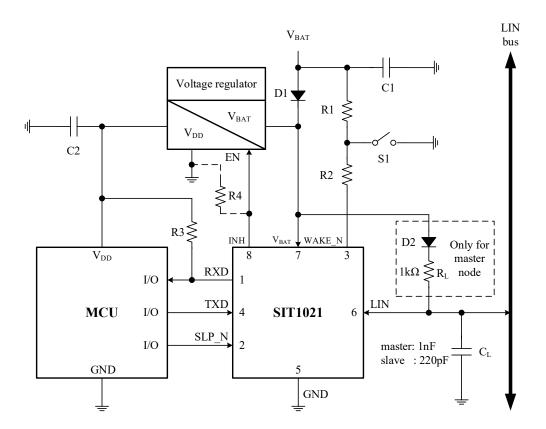

## TYPICAL APPLICATION

Fig 7. Typical application of the SIT1021

Note: To obtain a slower bus waveform slope, it is recommended to use a  $R_L/C_L$  combination of  $660\Omega/6.8nF$ , where  $R_L/C_L$  is the equivalent value of all nodes summarized. R4  $(10k\Omega\sim100k\Omega)$  is the drop-down resistance from INH to GND. Whether to add the pull-down resistance and its value should be selected according to the status of the EN pin of the external power supply chip.

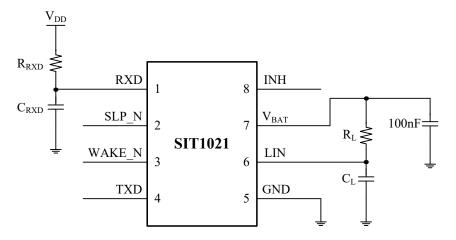

# TIMING TEST CIRCUIT

Fig 8. Timing test circuit for LIN transceiver

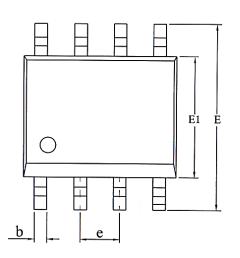

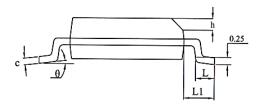

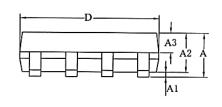

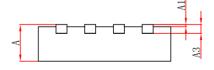

# **SOP8 DIMENSIONS**

#### **PACKAGE SIZE**

| TACKAGE SIZE |         |         |         |  |  |  |  |

|--------------|---------|---------|---------|--|--|--|--|

| SYMBOL       | MIN./mm | TYP./mm | MAX./mm |  |  |  |  |

| A            | 1.40    | -       | 1.80    |  |  |  |  |

| A1           | 0.10    | -       | 0.25    |  |  |  |  |

| A2           | 1.30    | 1.40    | 1.50    |  |  |  |  |

| A3           | 0.60    | 0.65    | 0.70    |  |  |  |  |

| b            | 0.38    | -       | 0.51    |  |  |  |  |

| D            | 4.80    | 4.90    | 5.00    |  |  |  |  |

| Е            | 5.80    | 6.00    | 6.20    |  |  |  |  |

| E1           | 3.80    | 3.90    | 4.00    |  |  |  |  |

| e            |         | 1.27BSC |         |  |  |  |  |

| h            | 0.25    | -       | 0.50    |  |  |  |  |

| L            | 0.40    | 0.60    | 0.80    |  |  |  |  |

| L1           |         | 1.05REF |         |  |  |  |  |

| С            | 0.20    | -       | 0.25    |  |  |  |  |

| θ            | 0°      | -       | 8°      |  |  |  |  |

LAND PATTERN EXAMPLE (Unit: mm)

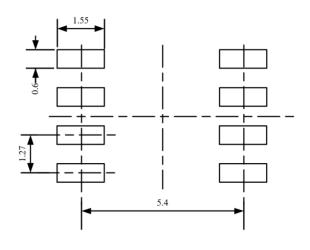

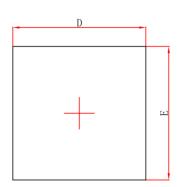

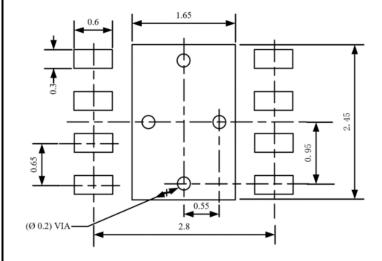

## DFN3\*3-8 DIMENSIONS

### PACKAGE SIZE

| SYMBOL | MIN./mm | TYP./mm   | MAX./mm |

|--------|---------|-----------|---------|

| A      | 0.70    |           | 0.80    |

| A1     | 0.00    | 0.02      | 0.05    |

| A3     |         | 0.203 REF |         |

| D      | 2.90    | 3.00      | 3.10    |

| Е      | 2.90    | 3.00      | 3.10    |

| D1     | 2.35    | 2.45      | 2.55    |

| E1     | 1.55    | 1.65      | 1.75    |

| b      | 0.2     | 0.25      | 0.33    |

| e      |         | 0.65 TYP  |         |

| L      | 0.35    |           | 0.45    |

LAND PATTERN EXAMPLE (Unit: mm)

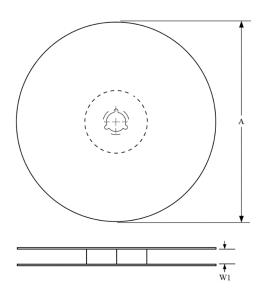

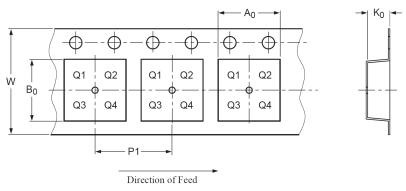

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the   |

|----|-----------------------------------------|

|    | component width                         |

| В0 | Dimension designed to accommodate the   |

|    | component length                        |

| K0 | Dimension designed to accommodate the   |

|    | component thickness                     |

| W  | Overall width of the carrier tape       |

| P1 | Pitch between successive cavity centers |

| 封装类型     | 卷盘直径<br>A (mm) | 编带宽度<br>W1 (mm) | A0 (mm)  | B0 (mm)   | K0<br>(mm) | P1 (mm)  | W<br>(mm) |

|----------|----------------|-----------------|----------|-----------|------------|----------|-----------|

| SOP8     | 330±1          | 12.4            | 6.60±0.1 | 5.30±0.10 | 1.90±0.1   | 8.00±0.1 | 12.00±0.1 |

| DFN3*3-8 | 329±1          | 12.4            | 3.30±0.1 | 3.30±0.1  | 1.10±0.1   | 8.00±0.1 | 12.00±0.3 |

PIN1 is in quadrant 1

# ORDERING INFORMATION

| TYPE NUMBER | PACKAGE                            | PACKING       |  |

|-------------|------------------------------------|---------------|--|

| SIT1021T    | SOP8                               | Tape and reel |  |

| SIT1021TK   | DFN3*3-8,<br>Small shape, no leads | Tape and reel |  |

SOP8 is packed with 2500 pieces/disc in braided packaging. Leadless DFN3\*3-8 is packed with 5000 pieces/disc in braided packaging.

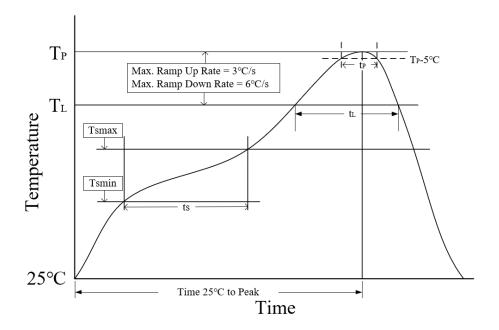

# REFLOW SOLDERING

| Parameter                                                             | Lead-free soldering conditions |  |

|-----------------------------------------------------------------------|--------------------------------|--|

| Ave ramp up rate $(T_L \text{ to } T_P)$                              | 3 °C/second max                |  |

| Preheat time ts                                                       | 60-120 seconds                 |  |

| $(T_{smin}=150  ^{\circ}\text{C to}  T_{smax}=200  ^{\circ}\text{C})$ |                                |  |

| Melting time t <sub>L</sub> (T <sub>L</sub> =217 °C)                  | 60-150 seconds                 |  |

| Peak temp T <sub>P</sub>                                              | 260-265 °C                     |  |

| 5°C below peak temperature t <sub>P</sub>                             | 30 seconds                     |  |

| Ave cooling rate (T <sub>P</sub> to T <sub>L</sub> )                  | 6 °C/second max                |  |

| Normal temperature 25°C to peak temperature                           | 8 minutes max                  |  |

| T <sub>P</sub> time                                                   |                                |  |

#### Important statement

SIT reserves the right to change the above-mentioned information without prior notice.

# REVISION HISTORY

| Version number | Data sheet status                                                     | Revision date     |  |

|----------------|-----------------------------------------------------------------------|-------------------|--|

| V1.0           | Initial version.                                                      | July 2020         |  |

| V1.1           | Add the internal block diagram of SIT1021;                            |                   |  |

|                | Modify the state transition diagram;                                  | January 2021      |  |

|                | Modify the remote wake-up sequence diagram.                           |                   |  |

|                | Added ESD test model description;                                     |                   |  |

|                | Modify the range of the IBAT indicator;                               | April 2021        |  |

| V1.2           | Modify the I <sub>BUS_PAS_rec</sub> indicator range;                  |                   |  |

|                | Modify the $I_{L(lob)}$ indicator range;                              |                   |  |

|                | Correct the temperature range.                                        |                   |  |

|                | Modify the limit parameter index;                                     |                   |  |

|                | Modify the range of the I <sub>BAT</sub> indicator;                   |                   |  |

|                | Modify the range of $V_{\text{BAT}}$ power-on and power-off threshold |                   |  |

| V1.3           | indicators; August 2                                                  |                   |  |

|                | Modify the range of the I <sub>BUS_PAS</sub> _dom indicator;          |                   |  |

|                | Modify the I <sub>BUS_NO_GND</sub> indicator range;                   |                   |  |

|                | Modify the R <sub>slave</sub> indicator range.                        |                   |  |

| V1.4           | Modified the range of V <sub>th(BAT)H</sub> indicator;                | November 2021     |  |

| V 1.4          | Added SIT1021 typical application load combination description.       | 140 VCIIIUCI 2021 |  |

| V1.5           | Modified package size information.                                    | January 2022      |  |

|                | Added "LAND PATTERN EXAMPLE";                                         |                   |  |

| V1.6           | Added tape information;                                               | April 2022        |  |

|                | Added reflow information.                                             |                   |  |

|                | Updated ordering information;                                         | January 2023      |  |

| V1.7           | Updated typical application diagram and added related application     |                   |  |

|                | descriptions.                                                         |                   |  |